# Hybridized PWM Strategy for Three- and Multiphase Three-Level NPC Inverters

Arkadiusz Lewicki D, Dmytro Kondratenko D, and Charles I. Odeh D

Abstract—A simple hybridized pulsewidth modulation (PWM) algorithm for three- and multiphase three-level neutral point clamped (NPC) inverters is proposed. The proposed solution is based on classical space vector PWM (SVPWM) algorithms for two-level inverters but can also be based on sinusoidal PWM with min-max injection. An additional level of output voltage is obtained by modifying the resulting switching patterns taking into account the actual dc-link voltages. In the case of SVPWM algorithms, such an approach eliminates the need to find the subsector where the reference voltage vector is located. It is also not necessary to analyze the changes in the position and length of active vectors in the case of dc-link voltage imbalance. DC-link voltage balancing is achieved by modifying the switching pattern, taking into account the values and direction of phase currents and actual dc-link voltages. Also, the algorithm optimizes the switching pattern and eliminates unnecessary switching instances. The proposed approach utilizes both space vector analysis and independent control of individual inverter-legs. The latter is peculiar to carrier-based PWM; hence, the proposed solution is termed hybridized PWM. Presented experimental tests and results validated the proposed control concept and algorithm for three- and multiphase NPC inverters.

Index Terms—DC-link voltage balancing, sinusoidal pulsewidth modulation (SPWM), space vector pulsewidth modulation (SVPWM), three-level NPC inverter.

## I. INTRODUCTION

HE properties of multilevel inverters make them interesting alternatives for two-level voltage source inverters (VSIs). Among multilevel inverter configurations, the most popular is the three-level diode-clamped neutral point clamped (NPC) inverter. This topology has been in existence since the early 1980s [1]. Compared to two-level VSIs, its output voltage

Manuscript received 23 January 2023; revised 11 July 2023 and 18 August 2023; accepted 21 September 2023. Date of publication 19 October 2023; date of current version 13 April 2024. This work was supported in part by the National Science Centre, Poland, under Grant 2021/41/N/ST7/01968. (Corresponding author: Dmytro Kondratenko.)

Arkadiusz Lewicki and Dmytro Kondratenko are with the Faculty of Electrical and Control Engineering, Gdańsk University of Technology, 80-233 Enugu, Poland (e-mail: arkadiusz.lewicki@pg.edu.pl; dmytro.kondratenko@pg.edu.pl).

Charles I. Odeh is with the Department of Electrical Engineering, University of Nigeria, Nsukka 410105, Nigeria (e-mail: charles.odeh@unn.edu.ng).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TIE.2023.3321999.

Digital Object Identifier 10.1109/TIE.2023.3321999

can be greater than the blocking voltage of the constituting power switches; the shape of its output voltage is closer to sinusoid; and the rate of voltage change (*du/dt*) is smaller. In the medium-voltage range, they can be a better replacement for classic two-level inverters [2]. For an obvious reason of low-cost power switches with low blocking voltage rating, they can be used also in low-voltage applications. The popularity of NPC inverters is evidenced by the presence of similar topologies: T-type [3], [4], [5]; F-type [6]; active NPC (ANPC) [7], and T-type ANPC [8] inverters.

Due to the diverse deployment of NPC inverters in various applications, their modulation/control algorithms have attained research maturity that allows them to be categorized. The modulation algorithms can basically be classified as: multicarrierbased sinusoidal pulse width modulation (SPWM) [9], [10]; selective harmonic elimination PWM (SHEPWM) [11], [12], [13]; and space vector pulsewidth modulation (SVPWM) [14], [15]. SVPWM and SPWM are the most popular modulation schemes for NPC [16], [17], [18], [19], [20]. The SVPWM algorithms are, however, more often utilized in multilevel inverters with a smaller number of levels (such as three-level inverters). As the number of levels increases, the SPWM algorithms are more likely used to control the inverter switches [10], [19], [21]. This is due to the difficulties in identifying the sectors and subsectors where the reference voltage vector is located in SVPWM [15], especially in the case of unbalanced dc-link voltages. Some of the SVPWM algorithms are dedicated to the correct generation of the output voltage in the case of unbalanced voltages [14].

DC-link voltage balancing methods in three-phase NPC inverters depend on the utilized modulation algorithms. The SHEPWM algorithms compute the switches' triggering instants to generate the output voltage with a desired harmonic content [11], [12], [13]. Such control methods are best suited for the steady-state operation of the inverter. Based on the load currents, the switching instants can also be computed to control the neutral-point potential of the dc link [22]. The angle computations of SHEPWM algorithms are determined based on the steady-state status and, thus, require knowledge of the load to determine the effects of the load currents on the dc-link voltages.

SVPWM algorithms are based on the combination of active vectors [14]. The dc-link voltages are controlled by activating the vectors that connect the load currents to the neutral point of dc-link capacitors. A similar effect can be obtained with the use of virtual vectors, which, in practice, are created by active vectors

with appropriate durations [23]. While the SVPWM control approaches ensure full dc-link voltage utilization and minimum harmonic content in the generated voltage waveform, the dc-link voltage balancing possibilities are restricted. The active vectors that can be used for balancing are assigned to the sectors where the output voltage vector is located [14]. This means that the balancing vectors must be predefined; and, in practice, the active vectors other than those assigned to the sectors are not utilized. Other solutions use discontinuous PWM methods to balance the dc-link capacitors [24]. This, in practice, allows to change the time of connecting the load current to the neutral point of the dc-link capacitor bank.

Control algorithms in SPWM are usually based on: introduction of the appropriate value of zero-sequence component to the reference voltage [25], [26]; forcing commutation between multiple voltage levels by modifying the modulating signal [27]; or adjusting the duty cycles in the phases operating in the multistep (MS) switching mode [28], [29]. Some of the solutions combine these methods: the common mode voltage reference is introduced to ensure an appropriate value of dc-link neutral point current; and the duty cycle in the phases operating in the MS switching mode is modified for further control of the dc-link current [9]. The limitation of these methods is related to relatively complicated algorithms. These methods necessitate the determination of the changes in the neutral point current given by the common mode voltage (to find the most appropriate value of common mode voltage with regard to dc-link voltage balancing). In turn, their great advantage is the ease of implementation in inverters with any number of phases [20], [25] compared to SVPWM methods.

Multiphase drives are recently becoming more and more popular. A single multiphase motor with quasi-rectangular rotor field distribution can operate with enhanced electromagnetic torque due to the use of higher current harmonics [30], [31]. A single multiphase VSI can be used to independently control several multiphase motors with sinusoidal rotor field distribution and phase transposition [32]. Such an application requires generating several output voltage vectors with independent rotating frequencies, positions, and lengths.

Classical approaches to SVPWM algorithms (usually used in three-phase inverters) require the determination of the sector where the reference voltage vector is located. The vector durations are determined for the active vectors surrounding this sector. The dc-link voltage can be optimally utilized if the vectors are well chosen (if they surround the sector).

In the case of multiphase inverters and the need to independently generate the reference voltage vectors in many orthogonal coordinate systems, the SVPWM algorithms are significantly complicated. If several reference voltage vectors have to be independently generated in a multiphase inverter, the calculation of the durations for the active vector nearest to the reference voltage vectors can deliver values greater than the switching period or even negative. This is because, in a multiphase VSI, all the active vectors in all the orthogonal spaces depend on one another.

Most proposed SVPWM solutions give the possibility of generating a reference voltage vector in only one coordinate system or many reference voltage vectors with a mutually dependent location. This enables the control of a single multiphase motor [33]. However, in drive systems where a single inverter controls a few motors independently, the reference voltage vectors should be generated independently [32], [34]. Consequently, the SPWM modulation schemes are usually used in such systems as simpler and less cumbersome control solutions [20].

In the case of three-level multiphase NPC inverters, the synthesis of space vectors requires the analysis of a large number of active vectors defined simultaneously in many orthogonal systems [35]. At the same time, the position and length of these vectors depend on the dc-link voltage asymmetry. Due to this, the direct or predictive torque control algorithms [36], [37] or SPWM control methods are often utilized [20].

Herein, a simple PWM algorithm for a three- and multiphase three-level NPC inverter with dc-link voltage balancing ability is proposed. In the case of three-level, three-phase NPC inverters, the proposed solution is based on the well-known SVPWM approach for three-phase two-level VSIs. In the case of multiphase, three-level NPC inverters, the proposed solution utilizes the SVPWM algorithm for multiphase two-level inverters proposed in [34]. Since the introduction of SPWM algorithms with min-max injection, the differences between the effects of SPWM and SVPWM have practically disappeared. This means that the proposed solution can also be based on SPWM with min-max injection.

While the durations of active and zero vectors are determined using SVPWM or SPWM methods, balancing the dc-link voltages is achieved by modifying the time of connecting the load current to the neutral point of the dc-link capacitors. In the last step of the algorithm, the obtained switching pattern is optimized to eliminate unnecessary switch transitions. For the fact that the algorithm is partly based on the SVPWM and partly uses the duty cycle control in each of the phases separately (as in SPWM methods), the control approach is termed hybridized PWM. In the following subsequent sections, analyses, experimental tests, and results carried out on both three- and five-phase three-level NPC inverters are presented.

#### II. SVPWM ALGORITHM

## A. SVPWM Algorithm for Two-Level VSIs

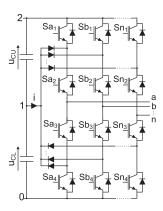

The main difference between a three-level and a two-level inverter topologies is the ability of using additional output voltage potential (the neutral point of the dc link). The three-level inverter can work as a two-level inverter if, in Fig. 1, both upper  $(S_{x1} \text{ and } S_{x2})$  or both lower switches  $(S_{x3} \text{ and } S_{x4})$  are activated simultaneously in individual phases. It is worth noting that the switching actions are complementary

$$S_{x3} = !S_{x1}; S_{x4} = !S_{x2} \tag{1}$$

where  $S_{x1...4}$  are the gate signals for the switches in the "x" phase  $(x = a \dots n)$ . The ON and OFF statuses of the switches are denoted with the numerals 1 and 0, respectively.

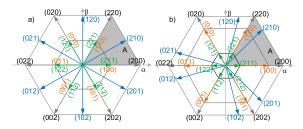

Active vectors in the three-phase, three-level NPC inverter form a regular hexagon, even in the case of dc voltage imbalance (see Fig. 2). In such cases, only the long active vectors (obtained

Fig. 1. *n*-phase three-level NPC inverter.

Fig. 2. SVD of a three-level, three-phase VSI. (a)  $u_{\rm CU}/u_{\rm CL}=1/1$ . (b)  $u_{\rm Cu}/u_{\rm CL}=0.3/0.7$ . A—one of the SVD sectors, and "012" are the output voltage potentials (see Fig. 1) in phases "a," "b," and "c."

for two-level operation) do not change their length and position. The position and length of medium active vectors (120,021,012, ...) or only the length of short active vectors (221, 110, 211, ....) (see Fig. 2) depend on the dc-link voltage imbalance. In the case of multiphase three-level NPC inverters, the number of available active vectors is greater and only the long active vectors (obtained for two-level operation) do not change their length and position. Similar to the three-phase VSIs, the parameters of medium and short active vectors depend on the dc-link voltage imbalance. The active vectors are simultaneously located in many orthogonal systems that generate additional problems in the implementation of SVPWM algorithms.

Classical SVPWM methods require indicating the sector and subsector in a space vector diagram (SVD), where the end of the reference voltage vector is located (see Fig. 2). In three-phase inverters, the active vectors adjacent to a given sector/subsector are selected to generate the output voltage. It should be noted that in the case of dc-link voltages imbalance, the shape of the sectors remains unchanged (long vectors do not change their position and length) while the shape of the subsectors is changing (see Fig. 2). Simplification of the SVPWM algorithm can, therefore, be obtained by synthesizing only the long active vectors, while the remaining vectors (short and/or medium) will be introduced by modifying the resulting switching pattern. In Fig. 2, for the reference voltage vector located in sector A, the duration of the long active vector (200) and (220) can be determined as

$$t_{(1)(200)} = T_{\text{sw}} \frac{u_{o\alpha} \cdot V_{\beta(220)} - u_{o\beta} \cdot V_{\alpha(220)}}{V_{\alpha(200)} \cdot V_{\beta(220)} - V_{\beta(200)} \cdot V_{\alpha(220)}}$$

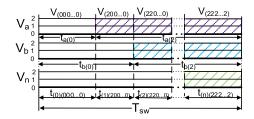

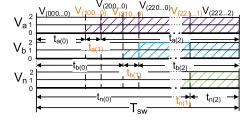

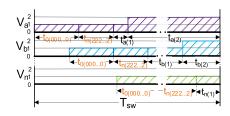

Fig. 3. Switching pattern of the three-level NPC inverter working in a two-level mode;  $V_a, \dots, V_n$ —output voltage potentials (see Fig. 1).

$$t_{(2)(220)} = T_{\text{sw}} \frac{-u_{o\alpha} \cdot V_{\beta(200)} + u_{o\beta} \cdot V_{\alpha(200)}}{V_{\alpha(200)} \cdot V_{\beta(220)} - V_{\beta(200)} \cdot V_{\alpha(220)}}$$

(2)

where  $u_{o\alpha}$ ,  $u_{o\beta}$  are the components of reference voltage vector,  $V_{\alpha(220)}$ ,  $V_{\beta(220)}$ ,  $V_{\alpha(200)}$ ,  $V_{\beta(200)}$  are the components of active long vectors surrounding sector A (see Fig. 2),  $T_{\rm sw}$  is a switching period represented by  $I/(2\cdot f_{\rm sw})$  in symmetrical PWM,  $f_{\rm sw}$  is the switching frequency, and  $t_{(1)(200)}$ ,  $t_{(2)(220)}$  are the active vector durations.

The duration of zero vectors (000) and (222) is determined as

$$t_{(0)(000)} = t_{(3)(222)} = 0.5 \cdot (T_{\text{sw}} - t_{(1)(200)} - t_{(2)(220)}).$$

(3)

Assuming that the zero vectors are located at the beginning and at the end of the switching pattern, the activation times for the pair of upper transistors in individual inverter phases "a"..."c" can be determined as (see Fig. 3)

$$t_{a(2)} = \sum_{i=0}^{3} a_i \cdot t_{(i)(abc)}; \dots; t_{c(2)} = \sum_{i=0}^{3} c_i \cdot t_{(i)(abc)}$$

(4)

where

$$a_i = 1 \Leftrightarrow t_{(i)(abc)} = t_{(2xx)}, \text{ else } a_i = 0$$

...

$$c_i = 1 \Leftrightarrow t_{(i)(abc)} = t_{(xx2)}, \text{ else } c_i = 0$$

(5)

and "x" – takes the value "2" or "0". Index 2 denotes the activation time of the potential "2" (see Fig. 1) in the VSI phases.

The determined time values can be directly used to generate the gate signals for inverter switches.

Similar results in the form of gate signal durations for a two-level multiphase VSI can be obtained using the SVPWM proposed in [34]. The duration of the "2" potential pulses [activated two upper transistors  $Sx_1$  and  $Sx_2$ , (x = a, ..., n)] in particular inverter phases is equal to (see Fig. 3)

$$t_{a(2)} = \sum_{i=0}^{n} a_i \cdot t_{(i)(abc...n)}, \dots, t_{n(2)} = \sum_{i=0}^{n} n_i \cdot t_{(i)(abc...n)}$$

(6)

where

$$a_i = 1 \Leftrightarrow t_{(i)(abc...n)} = t_{(2xx...x)}, \text{ else } a_i = 0$$

...

$$n_i = 1 \Leftrightarrow t_{(i)(abc...n)} = t_{(xxx...2)}, \text{ else } n_i = 0$$

(7)

Fig. 4. Switching pattern of the three-level NPC inverter with (111) zero vector.

and "x" can be "0" or "2," and  $t_{(i)(abc...n)}$  represents the duration of zero and active vectors.

The duration of the "0" potential pulses (activated two lower transistors) in particular inverter phases (see Fig. 1) can be determined as

$$t_{a(0)} = T_{sw} - t_{a(2)}, \dots, t_{n(0)} = T_{sw} - t_{n(2)}.$$

(8)

In the case of two-level modulation, the upper and lower switches are activated in pairs:  $S_{x1} = S_{x2}$  and  $S_{x3} = S_{x4}$  (see Fig. 1).

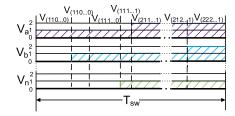

# B. SVPWM Algorithm for Three-Level VSIs

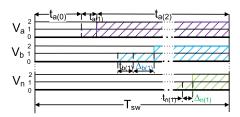

The switching pattern shown in Fig. 3 is for two-level operation. It is necessary to introduce an additional voltage level—the potential of the neutral point of dc-link capacitors ("1" in Fig. 1). This can be achieved by introducing an additional zero vector with the duration  $t_{(111\ldots 1)}$  into the switching pattern. Its duration can be any but not more than a sum of durations of existing zero vectors

$$0 \le t_{(111...1)} \le t_{(0)(000...0)} + t_{(n)(222...2)} \tag{9}$$

where the duration of zero vectors  $V_{(000...0)}$  and  $V_{(222...2)}$  is identical (3).

The resulting switching pattern for the multiphase NPC VSI will take the form shown in Fig. 4. The zero vector  $V_{(111\ldots 1)}$  will partially replace two zero vectors  $V_{(222\ldots 2)}$  and  $V_{(111\ldots 1)}$ . Due to further modifications of the switching sequence, it is convenient to adopt the duration of an additional zero vector closer to the lower limit of the range in (9).

Introducing an additional zero vector  $V_{(111\ldots 1)}$  (see Fig. 4) will cause additional switching operations into the switching pattern. However, it is possible to shift individual pulses with the potential "1" to reduce the number of additional switching operations. Because the duration of these pulses is the same in each inverter phase and equal to the zero vector duration  $t_{(111\ldots 1)}$

$$t_{a(1)} = t_{b(1)} = \dots = t_{n(1)} = t_{(111\dots 1)}$$

(10)

such an operation does not change the average value of the output voltage. The above operation requires the recalculation of the duration of the potentials "0" and "2"

$$t_{a(2)} = t_{a(2)} - t_{a(1)} \cdot 0.5, \quad \dots, \quad t_{n(2)} = t_{n(2)} - t_{n(1)} \cdot 0.5$$

$t_{a(0)} = t_{a(0)} - t_{a(1)} \cdot 0.5, \quad \dots, \quad t_{n(0)} = t_{n(0)} - t_{n(1)} \cdot 0.5.$

Fig. 5. Switching pattern of the three-level NPC inverter working in three-level mode after shifting the pulses of the (111) zero vector.

As a result, the additional active vectors  $V_{(100\ldots 0)}$ ,  $V_{(210\ldots 0)}\ldots V_{(222\ldots 1)}$  are obtained (see Fig. 5). It is worth noting that each of them connects the inverter load current to the neutral point of the dc-link capacitors. Since the durations of "1" pulses:  $t_{a(1)}\ldots t_{n(1)}$  are the same, it does not affect the balancing the dc-link voltages. Changing the durations of these pulses allows the control of the neutral-point potential.

# C. Balancing the DC-Link Voltages

The neutral point current affects the voltages on both dc-link capacitors (see Fig. 1)

$$u_{CU}\left(t\right) = \frac{1}{C} \int_{0}^{t} \left(\frac{i(\tau)}{2}\right) d\tau, \quad -u_{CL}\left(t\right) = \frac{1}{C} \int_{0}^{t} \left(\frac{i(\tau)}{2}\right) d\tau \tag{12}$$

hence, the difference between the voltages of the upper and lower capacitors is

$$\Delta u = u_{CU}(t) - u_{CL}(t) = \frac{1}{C} \int_0^t (i(\tau)) d\tau \qquad (13)$$

where "i" is a dc-link neutral-point current (see Fig. 1).

The coefficient  $q_{\rm act}$  specifies an actual voltage imbalance on the dc-link capacitors and can be determined from (13) as

$$q_{\rm act} = i \cdot t = C \cdot \Delta u \tag{14}$$

where "t" is the time to balance the voltages in dc link when the neutral point current is equal to "i." This current is supplied to the neutral point of the dc link by the individual inverter phases.

During the balancing process, the time of connecting the "0" and "2" potentials to the inverter terminals (see Fig. 1) is shortened, while the time of connecting the "1" potential is increased. Since the average value of the phase voltage cannot be changed, it is necessary to determine the range of these changes for each phase separately. The durations of "2" and "0" potentials can be reduced maximally by

if

$$(t_{x(2)} \cdot u_{CU} < t_{x(0)} \cdot u_{CL}) \Rightarrow t_{x(\max)} = t_{x(2)}$$

or

if  $(t_{x(0)} \cdot u_{CL} < t_{x(2)} \cdot u_{CU}) \Rightarrow t_{x(\max)} = t_{x(0)}$  (15)

where  $t_{x(2)}$  and  $t_{x(0)}$  are the times of generating the "2" and "0" potentials in phase "x" (x = a, b, ... n) (see Fig. 5) (11).

Because the durations of the potentials "2" and "0" are shortened at the same time, the charge "q" that can be supplied from individual inverter phases to the dc-link neutral point to

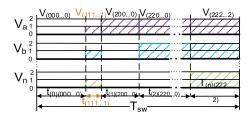

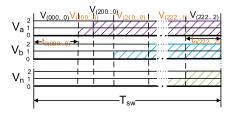

Fig. 6. Resulting switching pattern for  $i_a<0$ ,  $i_b>0$ ,  $i_c>0$  and  $u_{\rm CU}< u_{\rm CL}$  ( $\Delta_{1(a)}=0$ ).

counteract the dc-link voltage imbalance is equal to

$$q_{x(\max)} = 2 \cdot t_{x(\max)} \cdot i_x \tag{16}$$

taking into account the condition

if

$$\left(\operatorname{sgn}\left(q_{x(\max)}\right) \neq \operatorname{sgn}\left(q_{\operatorname{act}}\right)\right) \Rightarrow q_{x(\max)} = 0$$

(17)

where sgn() is sign(+ or -), and x is VSI phase  $(x = a, b, \ldots n)$ . Equation (17) prevents further increase in dc-link voltage imbalance.

The maximum charge that can be delivered to the dc-link neutral point can be determined as

$$q_{\text{all(max)(all)}} = \sum_{x=a}^{n} q_{x(\text{max})}$$

(18)

where "x" is an inverter phase, and n is the number of VSI phases.

The dc-link voltages can be balanced with the use of the charge supplied from individual inverter phases in any proportion. The solution proposed here uses the charge provided by individual phases according to the relation

$$q_{x(\text{bal})} = q_{x(\text{max})} \cdot \frac{q_{\text{act}}}{q_{\text{all(max)}}}, \quad x = a, b, \dots, n.$$

(19)

When a small charge is needed to balance the dc-link voltages  $0 \le \operatorname{abs}(q_{\operatorname{act}}) \le \operatorname{abs}(q_{\operatorname{all}(\max)})$ , they will be balanced in the current switching period  $T_{\operatorname{sw}}$ ; otherwise, it will take more than a single switching period using the maximum available charge (18).

In order to balance the dc-link voltages, the duration of "1" pulses in individual VSI phases has to be extended by the value (see Fig. 6)

$$\Delta_{x(1)} = \frac{q_{x(\text{bal})}}{i_x}.\tag{20}$$

While maintaining the unchanging average value of the phase voltages, the durations of the individual potentials (10), (11) must be corrected according to

$$\begin{split} t_{a(2)} &= t_{a(2)} - \Delta_{a(1)} \cdot \frac{u_{CL}}{u_{CL} + u_{CU}}, & t_{a(1)} &= t_{a(1)} + \Delta_{a(1)} \\ t_{a(0)} &= t_{a(0)} - \Delta_{a(1)} \cdot \frac{u_{CU}}{u_{CL} + u_{CU}} \end{split}$$

$$t_{n(2)} = t_{n(2)} - \Delta_{n(1)} \cdot \frac{u_{CL}}{u_{CL} + u_{CU}}, \quad t_{n(1)} = t_{n(1)} + \Delta_{n(1)}$$

$$t_{n(0)} = t_{n(0)} - \Delta_{n(1)} \cdot \frac{u_{CU}}{u_{CL} + u_{CU}}.$$

(21)

ig. 7. Resulting sequence of active and zero vectors.

Fig. 8. Switching pattern with replaced zero vectors.

Because of (15), the obtained times  $t_{x(0)} \dots t_{x(2)}$  will not be negative. The resulting switching pattern and utilized active vectors are shown in Fig. 7.

The average output phase voltage [in relation to the neutral dc-link point "1" (see Fig. 1)] will be equal to

$$\frac{1}{T_{\text{sw}}} \begin{pmatrix} \left( t_{x(2)} - \Delta_{x(1)} \cdot \frac{u_{CL}}{u_{CL} + u_{CU}} \right) \cdot u_{CU} + \left( t_{x(1)} + \Delta_{x(1)} \right) \cdot 0 \\ - \left( t_{x(0)} - \Delta_{x(1)} \cdot \frac{u_{CU}}{u_{CL} + u_{CU}} \right) \cdot u_{CL} \end{pmatrix} \\

= \frac{1}{T_{\text{cw}}} \left( t_{x(2)} \cdot u_{CU} - t_{x(0)} \cdot u_{CL} \right). \tag{22}$$

This means that the balancing procedure does not affect the average value of the obtained voltages.

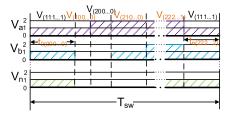

#### D. Optimization of Switching Pattern

The last step of the algorithm is optional and aims at optimizing the resulting switching pattern by reducing the number of switch commutations. This can be done by replacing the zero vectors  $V_{0(000\ldots 0)}$  and  $V_{n(222\ldots 2)}$  with a zero vector  $V_{(111\ldots 1)}$  (see Fig. 8). The durations of zero vectors  $V_{0(000\ldots 0)}$  and  $V_{n(222\ldots 2)}$  are equal to the shortest of  $t_{x(0)}$  times and to the shortest of  $t_{x(2)}$  times, respectively, where  $(x=a,b,\ldots,n)$

$$t_{0(000...0)} = t_{x(0)(\min)} = \min \left( t_{a(0)} \dots t_{n(0)} \right)$$

$$t_{n(222...2)} = t_{x(2)(\min)} = \min \left( t_{a(2)} \dots t_{n(2)} \right).$$

(23)

The switching pattern shown in Fig. 8 can be optimized by grouping the potentials "1," as shown in Fig. 9. This operation does not change the average value of the output voltage.

The durations  $t_{a(2)}, \ldots, t_{n(2)}$  and  $t_{a(0)}, \ldots, t_{n(0)}$  can be recalculated as

$$t_{a(0)} = t_{a(0)} - t_{0(000...0)}, \dots, t_{n(0)} = t_{n(0)} - t_{0(000...0)}$$

$$t_{a(2)} = t_{a(2)} - t_{n(222...2)}, \dots, t_{n(2)} = t_{n(2)} - t_{n(222...2)}$$

(24)

Optimization of the switching pattern.

Optimized sequence of active and zero vectors.

TABLE I EXPERIMENTAL SETUP SPECIFICATION

| Component             | Specification         |

|-----------------------|-----------------------|

| Capacitor banks       | $2x500\mu F$ , $600V$ |

| RL load               | $20\Omega$ , $20mH$   |

| Switching frequency   | 3.3 <i>kHz</i>        |

| Fundamental frequency | 50 <i>Hz</i>          |

| Power switches        | AIKW50N60C            |

while the durations  $t_{a(1)} \dots t_{n(1)}$  will be equal to

$$t_{a(1)} = t_{a(1)} + t_{0(000...0)} + t_{n(222...2)}$$

...

$$t_{n(1)} = t_{n(1)} + t_{0(000...0)} + t_{n(222...2)}.$$

(25)

The resulting switching pattern is shown in Fig. 9, and the sequence of space vectors is shown in Fig. 10. The gate signal durations of the switches' gate signals in Fig. 1 can be determined as

$$t_{Sx1} = t_{x(2)}, \ t_{Sx2} = t_{Sx3} = t_{x(1)}, \ t_{Sx4} = t_{x(0)}$$

(26)

where x = (a, b, ..., n) is the VSI phase.

The execution steps of the proposed algorithm are presented in Fig. 11.

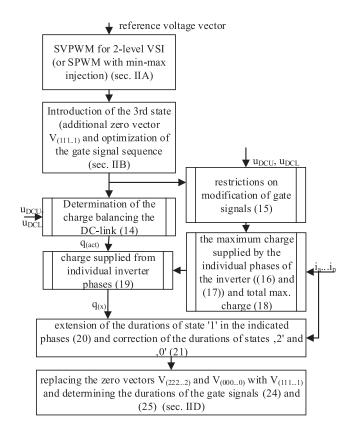

# III. EXPERIMENTAL RESULTS

Experimental tests were carried out using a five-phase 3L-NPC VSI, which can be configured to operate in three-phase and five-phase modes. The laboratory prototype of the inverter is shown in Fig. 12 and the load parameters are given in Table I. The inverter was supplied by an autotransformer. The voltage from it was set in such a way as to place 400 V in the dc link in no-load condition. The effect seen in experimental waveforms (see Fig. 13) is the effect of the autotransformer's inductance: a change in the load results in a slight voltage change.

Fig. 11. Flowchart for the proposed modulation and balancing algorithm.

Fig. 12. Laboratory prototype setup of the three-level, five-phase NPC inverter.

For comparison, the proposed modulation strategy and the carrier-based pulse width modulation (CBPWM) method shown in [9] have been implemented in the inverter processor. To validate the effectiveness of the proposed PWM technique, experimental studies were conducted for three-phase (see Figs. 13-21) and five-phase Figs. 22–25) modes.

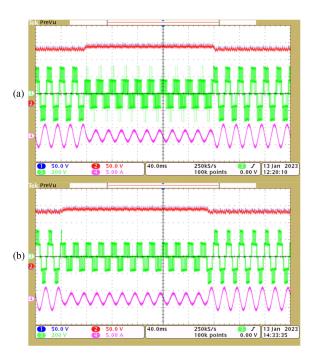

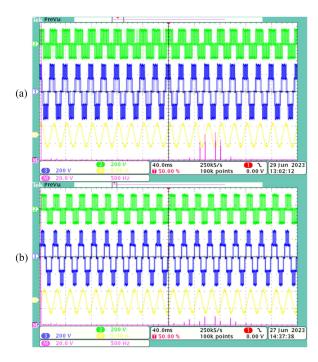

Fig. 13 displays the line-to-line voltage, output current, and dc-link voltages during a step change in the modulation index: from 1 to 0.5 and back to 1 again for both modulation methods. The output voltage waveform is generated correctly for both modulation techniques.

Fig. 13. Three-phase inverter step changes for the modulation indexes from 1 to 0.5 and back to 1. DC-link voltages: 1), 2) 50 V/div; line-to-line voltage: 3) 200 V/div; output current: 4) 5 A/div; time scale: 40 ms/div; output voltage frequency: 50 Hz. (a) Proposed PWM. (b) CBPWM.

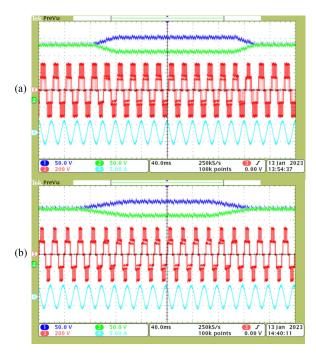

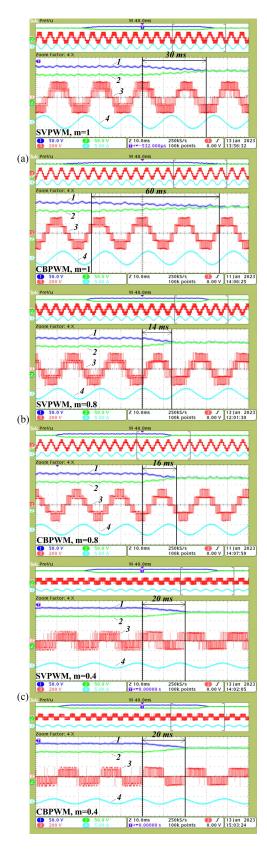

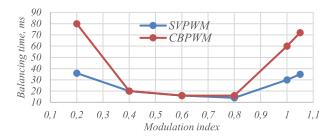

In Fig. 14, for the unity modulation index (m = 1), the changes in dc-link capacitor voltages obtained using both modulation methods are compared. In detail, the balancing algorithm performance under different modulation index conditions for proposed and conventional modulation methods is shown in Fig. 15 and compared in Fig. 16. The proposed method is characterized by the shorter time of dc-link voltage equalization over a wide range of modulation index values, except in the interval: m = 0.4, ..., m = 0.7, where the balancing speeds of both methods are similar.

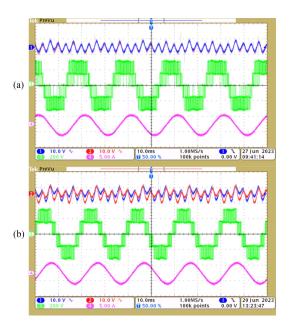

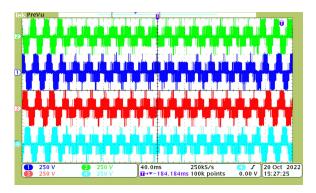

Fig. 17 presents the waveforms of a phase voltage, line-to-line voltage, and output current, as well as the results of harmonic analysis of line-to-line voltage obtained using the proposed [see Fig. 17(a)] method and CBPWM [see Fig. 17(b)]. For the proposed solution in steady-state operation, additional voltage levels in the output voltage waveforms can be observed. These additional levels are the effect of precise balancing of dc-link voltages. Even a small difference in the dc-link voltages results in a direct duration change of the potential "1" (20). When the dc-link voltages are close to being balanced, a small charge is required to be delivered to the capacitors. Consequently, only small duration changes of "1" potential (20) in the phases with the appropriate current directions are required. This makes the switching patterns contain all the states "0," "1," and "2" (see Fig. 6). In the proposed approach, the balancing charge is divided between all the phases (19) so it affects the changes in the durations of "1" potential. The charge division between phases does not take into account the duration of "2" and "0" pulses of individual legs. As a result, these durations remain different in individual inverter phases.

Fig. 14. Balancing algorithm performance for modulation index m=1. DC-link voltages: 1), 2) 50 V/div; line-to-line voltage: 3) 200 V/div; output current: 4) 5 A/div; time scale 40 ms/div; output voltage frequency: 50 Hz. (a) Proposed PWM. (b) CBPWM.

The final step of the algorithm (see Section II-D) is to optimize the obtained switching patterns. This optimization is based on replacing the zero vectors  $V_{0(000\ldots 0)}$  and  $V_{n(222\ldots 2)}$  with the zero vector  $V_{0(111\ldots 1)}$  and modifying the resulting switching patterns. This results in the elimination of the highest and the lowest voltage levels ("2" and "0") in at least one of the phase voltages. The rest of the phase voltages can be generated using all voltage levels.

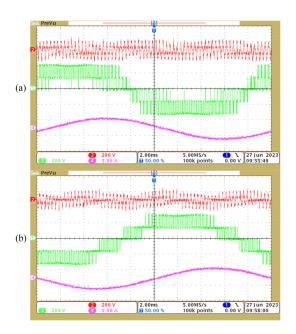

In order to show the properties of the proposed method, the ac components of dc-link voltages for the proposed PWM and CBPWM are compared in Fig. 18. The proposed control approach leads to precise dc-link voltage balancing, wherein the capacitor voltages are extremely close to each other. Conventional technique, on the other hand, provides differences in dc-link voltages, up to 4V [see Fig. 18(b)]. The comparison of the common mode voltage for both modulation methods is presented in Fig. 19. For both methods, the amplitudes of CMV are at the same level.

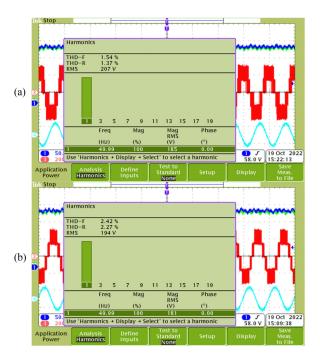

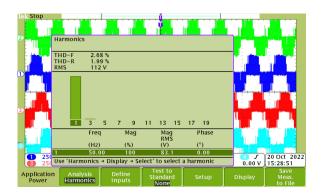

The harmonic spectra (up to 50th harmonic) of line-to-line voltages of both modulation methods are shown in Fig. 20 for the unity modulation index. Therin, THD values of 1.54% and 2.42% were obtained for the proposed algorithm and CBPWM modulation techniques, respectively. Additionally, THD values of 2.92% and 2.82% were obtained for the proposed algorithm and CBPWM modulation techniques, respectively, while the 100 harmonics (including switching frequency) were taken into consideration for analysis.

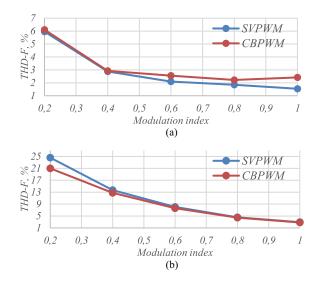

A plot of THD (up to 50th harmonic) versus modulation index is shown in Fig. 21(a). In this figure, THD values for

Balancing algorithm performance for modulation indexes: (a) m = 1; (b) m = 0.8; (c) m = 0.4. DC-link voltages: 1), 2) 50 V/div; line-to-line voltage: 3) 200 V/div; phase current: 4) 5 A/div; time scale: 20 ms/div; output voltage frequency: 50 Hz. Proposed PWM on the top and CBPWM on the bottom.

Balancing speed for the proposed PWM technique and conventional CBPWM with different modulation indexes.

Waveforms of the inverter phase voltage: 2) 200 V/div; lineto-line voltage: 3) 200 V/div; current: 4) 5 A/div; FFT analysis of the lineto-line voltages (20 V/div, 500 Hz/div) for (a) proposed and (b) CBPWM techniques. Time scale: 40 ms/div. Modulation index: m = 1.

both modulation methods are comparable for lower modulation indexes m < 0.45. Slight differences in THD values for the proposed and convenient modulation techniques may be noticed when the modulation index is higher than m = 0.5. Fig. 21(b) presents the plot of THD up to the 100th harmonic. Obtained THD values are comparable for higher modulation index m > 0.8. However, the CBPWM provides lower THD values in the modulation index range of 0.2 to 1. Switching frequency of 3.3 kHz was used for the analysis and THD calculation.

The computation time in three-phase configuration for hybrid PWM and for CBPWM techniques are 1.65  $\mu$ s and 1.79  $\mu$ s, respectively. Both algorithms were executed on the ADSP21363L DSP processor.

Figs. 22–25 present the experimental test results from the fivephase 3L NPC inverter with the proposed modulation method. Fig. 22 shows the output voltages during the step change of the modulation index. The voltage harmonic spectrum for a

Fig. 18. Waveforms of ac components of both dc-link voltages for the (a) proposed PWM strategy and (b) CBPWM. Modulation index: m=1; dc-link voltages: 1), 2) 10 V/div; output voltage: 3) 200 V/div; phase current: 4) 5 A/div; time scale 10 ms/div.

Fig. 19. Waveform of common mode voltage of the three-level, three-phase NPC inverter controlled using the (a) proposed modulation method and (b) CBPWM. CMV: 2) 200 V/div; line-to-line output voltage: 3) 200 V/div; output current: 4) 5 A/div; time scale: 2 ms/div.

modulation index of 1 is shown in Fig. 23. The THD value is 2.68%.

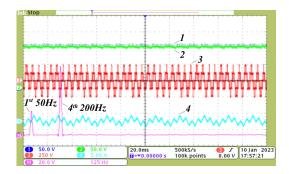

The possibility of dc-link voltages balancing in five-phase VSI is shown in Fig. 24. When only a single fundamental output voltage harmonic was generated with the unity modulation index, the balancing time was 18 ms [see Fig. 24(a)]. In the case

Fig. 20. FFT analysis (up to 50th harmonic) of the line-to-line voltages for the proposed and conventional modulation techniques; modulation index: m=1. DC-link voltages: 1), 2) 50 V/div; line-to-line voltage: 3) 200 V/div; output current: 4) 5 A/div; time scale: 20 ms/div. (a) Proposed PWM. (b) CBPWM.

Fig. 21. FFT analysis of the line-to-line voltages for the proposed PWM and conventional CBPWM modulation techniques. (a) Up to 50th harmonic. (b) Up to 100th harmonic.

of simultaneous generation of fundamental (1st),  $m_1 = 0.52$ , and additional (4th),  $m_4 = 0.87$ , output voltage harmonics, the balancing time was 22 ms [see Fig. 24(b)]. The waveforms of both dc-link voltages, phase current, and line-to-line voltage, as well as the fast Fourier transform (FFT) analysis of the line-to-line voltage, are shown in Fig. 25. The time of computation in the five-phase configuration for the proposed algorithm is 1.91  $\mu$ s.

Fig. 22. Five-phase inverter step changes in the modulation index from 1 to 0.5 and back to 1. Output voltage waveforms: 250 V/div, 40 ms/div.

Fig. 23. FFT analysis of the line-to-line voltage for the proposed hybrid modulation technique in a five-phase configuration; modulation index: m = 1.

Fig. 24. Balancing algorithm performance for the proposed hybrid modulation technique in five-phase configuration. (a) Fundamental (1st–50 Hz) harmonic only; modulation index: m=1. (b) 1st (50 Hz) and 4th (200 Hz) harmonics generation. DC-link voltages: 1), 2) 50 V/div; line-to-line voltage: 3) 250 V/div; output current: 4) 5 A/div, 10 ms/div.

Fig. 25. FFT analysis (M) of the line-to-line voltage 3), phase current 4), and dc-link voltages 1), 2) for the proposed hybrid modulation technique in five-phase configuration, with 1st (50 Hz) and 4th (200 Hz) harmonics generation. The modulation indexes: 0.52 and 0.87. Scale: dc-link voltages: 50 V/div; line-to-line voltage: 250 V/div; current: 5 A/div, 20 ms/div; harmonics 20 V/div, 125 Hz/div.

## IV. CONCLUSION

In this article, a simplified hybridized PWM strategy for three- and multiphase three-level NPC inverters was proposed. In the presented algorithm, the subsector searching problem was eliminated by treating the three-level inverter as a two-level inverter. The third level of the output voltage waveform is added by modifying the resulting switching pattern. The widths of these potential pulses are changed in the dc-link voltage balancing algorithm based on the energy-exchange concept. The resulting switching pattern is further optimized to reduce the number of commutations by modifying the zero vectors. The proposed modulation method was compared with the CBPWM technique for three-phase application. Compared to the CBPWM technique, the proposed modulation approach leads to faster and more precise balancing of the dc-link voltages. However, the switching losses are compromised since the commutation number is increased in the proposed solution. These features are the main advantages and disadvantages of the proposed hybrid PWM. The control approach was extended to multiphase, three-level NPC inverter operation. Laboratory tests were carried and experimental results were adequately presented for the five-phase, three-level NPC inverter.

### REFERENCES

- A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point-clamped PWM inverter," *IEEE Trans. Ind. Appl.*, vol. IA-17, no. 5, pp. 518–523, Sep. 1981, doi: 10.1109/TIA.1981.4503992.

- [2] J. Rodríguez, S. Bernet, B. Wu, J. O. Pontt, and S. Kouro, "Multi-level voltage-source-converter topologies for industrial medium-voltage drives," *IEEE Trans. Ind. Electron.*, vol. 54, no. 6, pp. 2930–2945, Dec. 2007, doi: 10.1109/TIE.2007.907044.

- [3] P. Knaup, "Inverter," Int. Patent Appl., WO 2007/048420 A1, May 3, 2007. [Online]. Available: https://patentscope.wipo.int/search/en/ detail.jsf?docId=WO2007048420

- [4] L. Ma, T. Kerekes, R. Teodorescu, X. Jin, D. Floricau, and M. Liserre, "The high efficiency transformer-less PV inverter topologies derived from NPC topology," in *Proc. 13th Eur. Conf. Power Electron. Appl.*, 2009, pp. 1–10.

- [5] L. Vancini, M. Mengoni, G. Rizzoli, L. Zarri, and A. Tani, "Voltage balancing of the DC-link capacitors in three-level T-type multiphase inverters," *IEEE Trans. Power Electron.*, vol. 37, no. 6, pp. 6450–6461, Jun. 2022, doi: 10.1109/TPEL.2021.3137083.

- [6] C. Odeh, A. Lewicki, M. Morawiec, and D. Kondratenko, "Three-level F-type inverter," *IEEE Trans. Power Electron.*, vol. 36, no. 10, pp. 11265–11275, Oct. 2021, doi: 10.1109/TPEL.2021.3071359.

- [7] Z. Shen, M. Chen, H. Wang, X. Wang, and F. Blaabjerg, "EMI filter robustness in three-level active neutral-point-clamped inverter," *IEEE Trans. Power Electron.*, vol. 37, no. 4, pp. 4641–4657, Apr. 2022, doi: 10.1109/TPEL.2021.3124282.

- [8] J. Pribadi and D. C. Lee, "A six-level T-type ANPC inverter for medium-voltage applications," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 2021, pp. 214–219, doi: 10.1109/APEC42165.2021.9487245.

- [9] A. Cervone, G. Brando, and O. Dordevic, "A hybrid modulation technique for the DC-bus voltage balancing in a three-phase NPC converter," in *Proc. Ind. Electron. Conf.*, 2019, pp. 3312–3318, doi: 10.1109/IECON.2019.8927047.

- [10] K. Wang, Z. Zheng, and Y. Li, "A novel carrier-overlapped PWM method for four-level neutral-point clamped converters," *IEEE Trans. Power Electron.*, vol. 34, no. 1, pp. 7–12, Jan. 2019, doi: 10.1109/TPEL.2018.2833148.

- [11] M. Sharifzadeh, H. Vahedi, A. Sheikholeslami, P. A. Labbé, and K. Al-Haddad, "Hybrid SHM-SHE modulation technique for a fourleg NPC inverter with DC capacitor self-voltage balancing," *IEEE Trans. Ind. Electron.*, vol. 62, no. 8, pp. 4890–4899, Aug. 2015, doi: 10.1109/TIE.2015.2405059.

- [12] M. Sharifzadeh et al., "Hybrid SHM-PWM for common-mode voltage reduction in three-phase three-level NPC inverter," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 9, no. 4, pp. 4826–4838, Aug. 2021, doi: 10.1109/JESTPE.2020.3037283.

- [13] M. Sharifzadeh, G. Chouinard, and K. Al-Haddad, "Compatible selective harmonic elimination for three-phase four-wire NPC inverter with DC-link capacitor voltage balancing," *IEEE Trans. Ind. Inform.*, to be published, doi: 10.1109/TII.2019.2934467.

- [14] A. Lewicki, Z. Krzeminski, and H. Abu-Rub, "Space-vector pulsewidth modulation for three-level NPC converter with the neutral point voltage control," *IEEE Trans. Ind. Electron.*, vol. 58, no. 11, pp. 5076–5086, Nov. 2011, doi: 10.1109/TIE.2011.2119453.

- [15] F. Chen, W. Qiao, H. Wang, and L. Qu, "Computation-cost-invariant universal space-vector pulse-width modulation for multilevel inverters," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2021, vol. 2, pp. 3460–3467, doi: 10.1109/ecce47101.2021.9595923.

- [16] V. Jayakumar, B. Chokkalingam, and J. L. Munda, "A comprehensive review on space vector modulation techniques for neutral point clamped multi-level inverters," *IEEE Access*, vol. 9, pp. 112104–112144, 2021, doi: 10.1109/ACCESS.2021.3100346.

- [17] R. Sarker, "Phase disposition PWM (PD-PWM) technique to minimize WTHD from a three-phase NPC multilevel voltage source inverter," in *Proc. IEEE Int. Conf. Converg. Eng.*, 2020, pp. 220–224, doi: 10.1109/ICCE50343.2020.9290697.

- [18] S. Busquets-Monge et al., "Multibattery-fed neutral-point-clamped DC-AC converter with SoC balancing control to maximize capacity utilization," *IEEE Trans. Ind. Electron.*, vol. 67, no. 1, pp. 16–27, Jan. 2020, doi: 10.1109/TIE.2019.2896176.

- [19] U. A. Sipai and P. N. Tekwani, "Capacitor voltage balancing for five-level neutral-point clamped inverter using modified carrier waves for carrierbased PWM technique," in *Proc. IEEE 16th India Council Int. Conf.*, 2019, pp. 4–7, doi: 10.1109/INDICON47234.2019.9028994.

- [20] A. Cervone, G. Brando, and O. Dordevic, "Hybrid modulation technique with DC-bus voltage control for multiphase NPC converters," *IEEE Trans. Power Electron.*, vol. 35, no. 12, pp. 13528–13539, Dec. 2020, doi: doi: 10.1109/TPEL.2020.2992226.

- [21] S. Kundu, S. K. Giri, S. Mukherjee, and S. Banerjee, "Performance analysis of three-phase five-level NPC inverter by using triangular and trapezoidal triangular carrier-based modulation techniques," in *Proc. IEEE 4th Int. Conf. Power, Control Embed. Syst.*, 2017, pp. 1–6, doi: 10.1109/ICPCES.2017.8117650.

- [22] A. Sanchez-Ruiz et al., "DC-link neutral point control for 3L-NPC converters utilizing selective harmonic elimination PWM," *IEEE Trans. Ind. Electron.*, vol. 69, no. 9, pp. 8633–8864, Sep. 2022, doi: 10.1109/TIE.2021.3113019.

- [23] F. Guo, T. Yang, S. Bozhko, and P. Wheeler, "3L-NPC AC-DC power converter using virtual space vector PWM with optimal switching sequence based on g-h coordinate," in *Proc. IEEE Int. Conf. Electr. Syst. Aircraft, Railway, Ship Propulsion Road Veh. Int. Transp. Electrif. Conf.*, 2019, pp. 1–7, doi: 10.1109/ESARS-ITEC.2018.8607586.

- [24] J. S. Lee, S. Yoo, and K. B. Lee, "Novel discontinuous PWM method of a three-level inverter for neutral-point voltage ripple reduction," *IEEE Trans. Ind. Electron.*, vol. 63, no. 6, pp. 3344–3354, Jun. 2016, doi: 10.1109/TIE.2016.2530038.

- [25] I. López et al., "Generalized PWM-based method for multiphase neutral-point-clamped converters with capacitor voltage balance capability," *IEEE Trans. Power Electron.*, vol. 32, no. 6, pp. 4878–4890, Jun. 2017, doi: 10.1109/TPEL.2016.2599872.

- [26] J. Pou et al., "Fast-processing modulation strategy for the neutral-point-champed converter with total elimination of low-frequency voltage oscillations in the neutral point," *IEEE Trans. Ind. Electron.*, vol. 54, no. 4, pp. 2288–2294, Aug. 2007, doi: 10.1109/TIE.2007.894788.

- [27] K. Wang, Z. Zheng, L. Xu, and Y. Li, "A generalized carrier-overlapped PWM method for neutral-point-clamped multilevel converters," *IEEE Trans. Power Electron.*, vol. 35, no. 9, pp. 9095–9106, Sep. 2020, doi: 10.1109/TPEL.2020.2969548.

- [28] W. Jiang, X. Huang, J. Wang, J. Wang, and J. Li, "A carrier-based PWM strategy providing neutral-point voltage oscillation elimination for multi-phase neutral point clamped 3-level inverter," *IEEE Access*, vol. 7, pp. 124066–124076, 2019, doi: 10.1109/ACCESS.2019.2938623.

- [29] I. Lopez et al., "Modulation strategy for multiphase neutral-point-clamped converters," *IEEE Trans. Power Electron.*, vol. 31, no. 2, pp. 928–941, Feb. 2016, doi: 10.1109/TPEL.2015.2416911.

- [30] E. Levi, R. Bojoi, F. Profumo, H. A. Toliyat, and S. Williamson, "Multiphase induction motor drives - A technology status review," *IET Electr. Power Appl.*, vol. 1, no. 4, pp. 489–516, 2007, doi: 10.1049/iet-epa:20060342.

- [31] J. Zhang, S. J. He, and K. A. I. Wang, "Multi-harmonic currents control strategy for five-phase permanent magnet machine with non-sinusoidal back-EMF," *IEEE Access*, to be published, doi: 10.1109/access.2020. 2989323.

- [32] E. Levi, R. Bojoi, F. Profumo, H. A. Toliyat, and S. Williamson, "Multiphase induction motor drives-A technology status review," *IET Electr. Power Appl.*, vol. 1, no. 5, pp. 643–656, 2007, doi: 10.1049/iet-epa.

- [33] C. Yong and H. Qiu-Liang, "Four-dimensional space vector PWM strategy for five-phase voltage source inverter," *IEEE Access*, vol. 7, pp. 59013–59021, 2019, doi: 10.1109/ACCESS.2019.2912178.

- [34] A. Lewicki, C. I. Odeh, D. Kondratenko, and M. Morawiec, "Hybridized space-vector pulse width modulation for multiphase two-level voltage source inverter," *IEEE Trans. Power Electron.*, vol. 37, no. 7, pp. 7663–7674, Jul. 2022, doi: 10.1109/TPEL.2022.3145161.

- [35] W. Song, M. S. R. Saeed, B. Yu, J. Li, and Y. Guo, "Model predictive current control with reduced complexity for five-phase three-level NPC voltage-source inverters," *IEEE Trans. Transp. Electrif.*, vol. 8, no. 2, pp. 1906–1917, Jun. 2022, doi: 10.1109/tte.2021.3131420.

- [36] B. Chikondra, U. R. Muduli, and R. K. Behera, "Improved DTC technique for THL-NPC VSI fed five-phase induction motor drive based on VVs assessment over a wide speed range," *IEEE Trans. Power Electron.*, vol. 37, no. 2, pp. 1972–1981, Feb. 2022, doi: 10.1109/TPEL.2021.3102963.

- [37] A. Bhowate, M. V. Aware, and S. Sharma, "Speed sensor-less predictive torque control for five-phase induction motor drive using synthetic voltage vectors," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 9, no. 3, pp. 2698–2709, Jun. 2021, doi: 10.1109/JESTPE.2020.3016335.

**Arkadiusz Lewicki** received the Ph.D. and D.Sc. degrees in electrical drives from the Faculty of Electrical Engineering, Gdansk University of Technology, Gdansk, Poland, in 2003 and 2013, respectively.

He is currently with the Institute of Automatic Control of Electric Drives, Gdansk University of Technology. His scientific activities are concentrated on microprocessor control of converters, multilevel converters, pulsewidth modulation techniques, and nonlinear control of drive systems.

Dmytro Kondratenko received the B.S. degree in automation and computer-integrated technologies from the National Technical University of Ukraine, Igor Sikorsky Kyiv Polytechnic Institute, Kyiv, Ukraine, in 2017 and the M.S. degree in automation, electronic, and electrical engineering from the Gdansk University of Technology, Gdansk, Poland, in 2019.

His research interests are concentrated on pulsewidth modulation techniques, multilevel converters, multiphase converters, nonlinear

control of drive systems, and adaptive control systems.

Charles I. Odeh received the B.Eng., M.Eng., and the Ph.D. degrees in electrical engineering from the University of Nigeria, Nsukka, Nigeria, in 2002, 2006, and 2010, respectively.

His fields of interest include multilevel converter topologies and pulsewidth modulation techniques.