# A nine-input 1.25 mW, 34 ns CMOS analog median filter for image processing in real time

W. Jendernalik · G. Blakiewicz · J. Jakusz · S. Szczepański

Received: 10 January 2013/Revised: 29 May 2013/Accepted: 20 June 2013/Published online: 29 June 2013 © The Author(s) 2013. This article is published with open access at Springerlink.com

**Abstract** In this paper an analog voltage-mode median filter, which operates on a  $3 \times 3$  kernel is presented. The filter is implemented in a 0.35 µm CMOS technology. The proposed solution is based on voltage comparators and a bubble sort configuration. As a result, a fast (34 ns) time response with low power consumption (1.25 mW for 3.3 V) is achieved. The key advantage of the configuration is relatively high accuracy of signal processing, which allows the calculation of the median of signals with the difference in amplitude as small as 10 mV. This feature allows the application of the filter to vision systems with up to 7 bit equivalent resolution. The analytical and statistical analysis of the filter resolution, and analysis of its speed limitations are presented and compared to measurement results. Based on the achieved results, a set of guidelines for the filter design and optimisation is presented.

**Keywords** Analog CMOS circuits · Early vision processing · Median filters · Low-power

## 1 Introduction

The median filtering is a non-linear operation frequently used in early vision image processing [1]. This kind of filtering allows for removing of high frequency impulsive noise, while preserving sharp edges in an original image. For this reason, the median filtering greatly facilitates further image processing such as the edge detection or the

segmentation. In integrated circuits, the median filters are implemented using both analog [2-16] and digital [17-20] techniques, depending on the design requirements. Typically, the greatest reduction of consumed power and required chip area are achievable using analog median filters, because they do not require analog to digital converters (ADC) for conversion of video signals generated by photo sensors. Whereas, digital filters require dedicated ADC for each analog video signal, which for a  $3 \times 3$ kernel means nine additional converters. Alternatively, a single fast converter multiplexed between nine inputs can be used, but such an approach reduces an overall image processing speed. Because, the number of ADCs increases with the square of the kernel size, the digital approach leads to excessively large circuit solutions, that consume relatively high power. The analog implementations of the median filters are simpler in construction, consumes less power, and are much faster, but have limited accuracy of signal processing. Therefore, if the application of a median filter is targeted at a video system with low or moderate dynamics, it is advantageous to use the analog filters. However, a particular attention should be paid to optimisation of the accuracy of such filters.

One of the methods used to obtain the median value, both in the digital or analog realizations, is a bubble sorting. This method leads to a simple and intuitive filter structure [2, 5]. On the other hand the filter complexity increases significantly with the number of inputs. In this paper an area-efficient implementation of a nine-input analog precise median filter, using the bubble sort is proposed.

Section 2 presents the configuration and the principle of operation of the proposed analog median filter. It is presented a circuit solution and analysis of its limitations and nonidealities. Section 3 is devoted to details of the filter

Department of Microelectronic Systems, Gdansk University of Technology, 80-233 Gdansk, Poland

e-mail: waldi@ue.eti.pg.gda.pl; waldi@eti.pg.gda.pl

W. Jendernalik ( $\boxtimes$ ) · G. Blakiewicz · J. Jakusz · S. Szczepański

implementation in a 0.35 µm CMOS technology, and results of simulation and measurements. The final conclusions are presented in the last section.

# 2 Median filter

# 2.1 General configuration and principle of operation

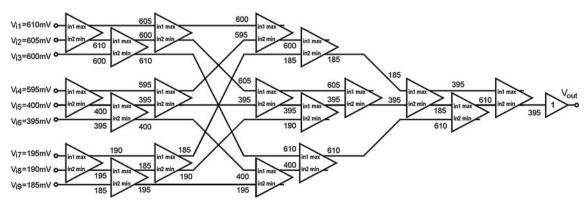

The bubble sort configuration, shown in Fig. 1, is adopted for implementation of the median filter. The circuit consists of 19 MAXMIN selector circuits and an output buffer. Each MAXMIN circuit has two inputs  $V_{in1}$  and  $V_{in2}$ , and two outputs  $V_{\rm max}$  and  $V_{\rm min}$ . The output signals depend on instantaneous values of the inputs, according to the following relationships

$$\begin{aligned} V_{\text{max}} &= V_{\text{in1}} \\ V_{\text{min}} &= V_{\text{in2}} \end{aligned} \end{aligned} \qquad \text{when } V_{\text{in1}} > V_{\text{in2}}$$

$$V_{\text{max}} &= V_{\text{in2}} \\ V_{\text{min}} &= V_{\text{in1}} \end{aligned} \end{aligned} \qquad \text{when } V_{\text{in1}} < V_{\text{in2}}$$

$$(1)$$

As (1) shows, MAXMIN selects the maximum input value and transmits it to the output labelled  $V_{\text{max}}$ . Analogously, the minimum input value is directed to the output  $V_{\min}$ . As a result, 19 MAXMIN selectors realize the bubble sort algorithm with the output voltage  $V_{\text{out}}$  being a median of all nine inputs  $V_{i1}...V_{i9}$

$$V_{\text{out}} = MED\{V_{i1}, V_{i2}, \dots, V_{i9}\}$$

(2)

The exemplary decisions (the node voltages) of the comparators, labelled in Fig. 1, have been deliberately marked incorrectly, to show the influence of the comparators input offset voltage on the final result. This issue will be explained in detail in Sect. 2.2.

The topology, shown in Fig. 1, has several advantages in comparison to other median filters presented in the literature [2, 4, 5, 11, 13]. First of all, the proposed median filter

is devoid of negative feedback loops, which guarantees the stability, and an aperiodic time response. Secondly, the circuit implementation of MAXMIN is simple, and can be based on a voltage comparator and an analog multiplexer. And finally, due to the configuration in Fig. 1 has only forward paths, its time response is very fast. The filter structure in Fig. 1 can be easily expanded to a general rank order filter by adding eight comparators.

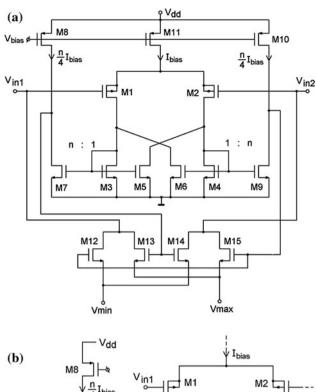

The MAXMIN circuit is designed using a differential two stage voltage comparator, which controls an analog multiplexer composed of four MOS switches. Figure 2 shows details of the circuit. The differential pair M1–M2, together with the active cross-coupled load M3-M6 make an input stage of the comparator. Such a configuration ensures a good stabilization of the common-mode output voltages and a relatively high differential gain. The output stages, on transistors M7-M8 and M9-M10, generate balanced signals, which directly control the switches M12-M15. It is worth to notice, that the series resistance of those switches does not affect the function (1) of the circuit, because in a steady state condition there is no current flow between the filter inputs  $V_{i1}...V_{i9}$  and the output  $V_{out}$ , and consequently there is no voltage drop. In other words, the output  $V_{\text{out}}$  in a steady state is an exact replica of one of the input signals.

# 2.2 Circuit limitations and nonidealities

#### 2.2.1 Corner errors

The analog implementation of the filter in Fig. 1 has a limited resolution in distinguishing values of the input signals  $V_{i1}...V_{i9}$ . This feature is called corner error [9, 12], and is the main cause of erroneous calculation of the median value at the filter output. A unique feature of the proposed circuit solution (Fig. 2) is that it does not cause any distortions of the processed video signals. Nonidealities of the MAXMIN circuits may lead to an incorrect

Fig. 1 Block diagram of an analog median filter

Fig. 2 MAXMIN selector circuit: a schematic, b parasitic components

choice from the set of the input signals, however the output value is always exactly equal to one of the inputs. To explain this feature, consider the sample input sequence shown in Fig. 1, where the input instantaneous values are: 610, 605, 600, 595, 400, 395, 195, 190, and 185 mV. In this input set, there are two values, namely 390 and 400 mV, which are close to each other, and also are close to the correct median value 400 mV. The remaining values are similar to each other but are spaced from the median. In the ideal case, the output of the filter should be equal to  $V_{i5} = 400$  mV. However, in a real circuit, in which the comparators may have an input offset voltage  $V_{OS}$  there will appear several incorrect decisions. An example of such a situation is illustrated in Fig. 1, where the actual output value is  $V_{i6} = 395$  mV, assuming that  $V_{OS} = \pm 10$  mV is randomly assign to individual comparators. It can be demonstrated that regardless of the input sequence order, the filter output signal reaches one of the two values  $V_{i6}$  or  $V_{i5}$ . This example shows that the total resolution of the filter is limited by the greatest input offset voltage of all comparators used.

In order to achieve high accuracy of signal processing, the limitations and nonidealities resulting from the MAX-MIN circuit must be analysed, and carefully minimised. As explained, the only cause of errors in the topology shown in Fig. 1 is incorrect classification of signals by the voltage comparators. There are two main sources of errors in the comparator, an input offset voltage and a transmission delay. The input offset voltage can be evaluated by adding both components, due to the differential pair (M1–M2), and the cross-coupled load (M3-M6). The voltage offsets, caused by the output stages composed of M7-M8 and M9-M10, are omitted, due to their small relative values. It is because, the output stage offsets are divided by a large gain of the first stage when referred to the comparator input. The input offset voltage of the differential pair results mainly from the threshold voltage mismatch [21, 22] which is

$$V_{\text{OS}12} = (\Delta V_T)_{1,2} \tag{3}$$

where  $(\Delta V_T)_{1,2}$  denotes the mismatch between the threshold voltages of M1 and M2. In (3) the transconductance parameter mismatch is omitted due to its relatively low impact [21] on the total input offset voltage. The contribution of the load to the offset voltage, referred to the input, is determined as a current mismatches  $(\Delta I_{\rm DS})_{5,6}$  and  $(\Delta I_{\rm DS})_{3,4}$ , between two pairs M5–M6 and M3–M4, divided by the voltage-current gain  $g_{m1,2}$  of the differential pair, which results in

$$V_{\text{OS3-6}} = \frac{(\Delta I_{\text{DS}})_{5,6} + (\Delta I_{\text{DS}})_{3,4}}{g_{\text{m1.2}}} \tag{4}$$

Assuming the square-low voltage-current characteristic  $I_{DS} = K_{PP(N)}(W/L)(V_{GS} - V_T)^2$  for the transistors, the total input offset  $V_{OS}$  of the comparator can be expressed as

$$V_{\text{OS}} = V_{\text{OS}1,2} + V_{\text{OS}3-6}$$

$$= (\Delta V_T)_{1,2} + \frac{(V_{\text{GS}} - V_T)_{1,2}}{(V_{\text{GS}} - V_T)_{5,6}} (\Delta V_T)_{5,6}$$

$$+ \frac{(V_{\text{GS}} - V_T)_{1,2}}{(V_{\text{GS}} - V_T)_{3,4}} (\Delta V_T)_{3,4}$$

(5)

where  $(\Delta V_T)_{5,6}$  and  $(\Delta V_T)_{3,4}$  represent the mismatches of the threshold voltages between M5–M6 and M3–M4. The threshold voltage mismatch can be expressed in terms of the standard deviation  $\sigma$  by means of the Pelgrom's formula [23, 21]

$$\sigma(\Delta V_{\rm GS}) = \frac{A_{V_T}}{\sqrt{WL}} \tag{6}$$

where  $A_{V_T}$  is a parameter specific for a selected technology. Assuming that  $V_{OS1,2}$  and  $V_{OS3-6}$  are statistically independent and  $(\Delta V_T)_{5.6} = (\Delta V_T)_{3.4}$ , the input offset voltage of the comparator, in Fig. 2 can be expressed as

$$V_{\rm OS} = \sqrt{\left(\frac{A_{V_{T^p}MOS}}{\sqrt{WL}}\right)_{1,2}^2 + 2\frac{K_{\rm PN}}{K_{\rm PP}} \left(\frac{L}{W}\right)_{1,2} \left(\frac{A_{V_{T^n}MOS}}{L}\right)_{3,4}^2}$$

(7)

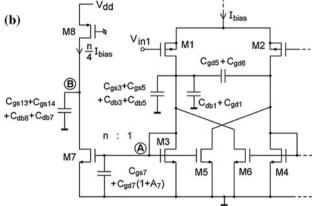

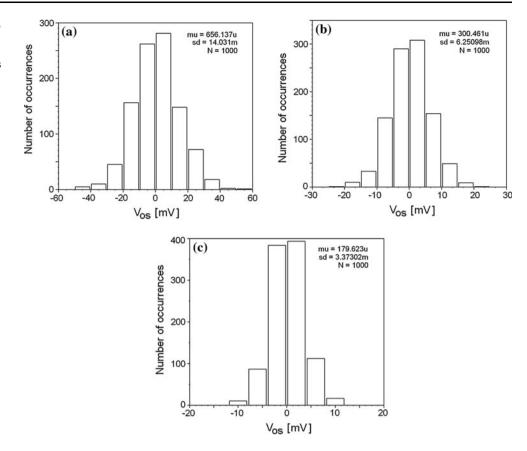

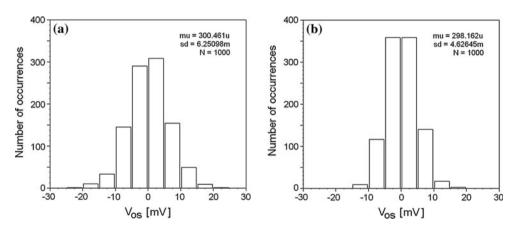

As (7) shows, the reduction of  $V_{OS}$  requires the application of M1 and M2 with a channel width as large as possible, and M3-M6 with the maximum possible channel length. To demonstrate the importance of a proper selection of the transistors width, let us consider three cases: (a)  $(W/L)_{1,2} = 2/1$ , (b)  $(W/L)_{1,2} = 10/1$ , (c)  $(W/L)_{1,2} = 50/1$ , where  $(W/L)_{3.4(5.6)} = 2/1$ . Using (7) and technology parameters specific for AMS 0.35 µm CMOS process, namely  $A_{V_T pMOS} = 10.3 \text{ mV } \mu\text{m}$ ,  $A_{V_T pMOS} = 6.7 \text{ mV } \mu\text{m}$ ,  $K_{PP} = 58 \,\mu\text{A/V}^2$ ,  $K_{PN} = 170 \,\mu\text{A/V}^2$  the input offset voltage  $V_{OS}$  are as follows: (a) 13.6 mV, (b) 6.1 mV, (c) 2.7 mV. The results of the Monte Carlo analysis are presented in Fig. 3, where the symbols mean: mu—the mean value, sd—the standard deviation, and N—the number of samples used. The achieved results show that the standard deviation of the input offset voltage are: (a) 14 mV, (b) 6.25 mV, (c) 3.37 mV, respectively for the considered cases. The offsets achieved from the simulations are a little bigger, because in this case both the threshold voltage and the propagation time of each signal depends on the path. which it passes. In the worst case, this time is equal to nine delays of a single MAXMIN circuit. The propagation delay of MAXMIN consists of the delay introduced by the comparator and the delay of the analog multiplexer. The propagation delay time of the comparator is estimated under assumption that the input differential signal is big enough to fully switch on one of the transistors M1 or M2 (Fig. 2a), causing the biasing current  $I_{\text{bias}}$  to flow through one of them. The circuit configuration relevant to this case is shown in Fig. 2(b). The propagation time can be estimated as a sum of two components: (i) the delay  $t_{\text{delay},A}$  between the input and the node labelled A, and (ii) the delay  $t_{\text{delay},B}$  between the node labelled A and B (the comparator output).

$$t_{\text{delay}} = t_{\text{delay},A} + t_{\text{delay},B} = \frac{0.5\Delta V_A}{SR_A} + \frac{0.5\Delta V_B}{SR_B} = \frac{0.5\Delta V_A}{SR_A} + \frac{0.5V_{DD}}{SR_B}$$

(8)

where:  $\Delta V_A$  and  $\Delta V_B$  denote the voltage swings at nodes A and B,  $SR_A$  and  $SR_B$  are the slew rates at the same nodes.  $SR_A$  depends on the biasing current  $I_{\text{bias}}$  and the total capacitance of the node A, which results inwhere  $A7 = gm7/(g_{ds7} + g_{ds8})$  is the voltage gain of M7. The positive and negative slew rates at the node B is determined respectively by the drain current of M8 and M7, and the total capacitance of this node, which leads to

$$SR_A^+ = SR_A^- = \frac{I_{\text{bias}}}{2C_{gs3-6} + C_{gs7} + 2C_{db3-6} + C_{db1} + (1 + A_7)C_{gd7} + C_{gd1} + 4C_{gd3-6}}$$

(9)

transconductance parameter mismatches are taken into account. The plots clearly show, that the input differential pair has a dominant influence on the total input offset voltage. This voltage can be reduced by using wide channel transistors and design the differential pair in the common-centroid manner.

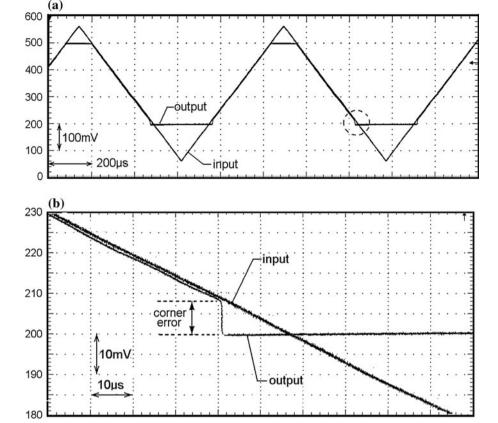

The comparison of the input offset voltage is presented in Fig. 4 for two cases: (a) M1 and M2 design as separate devices, and (b) M1 and M2 design in a common-centroid layout. As the histograms show, the common-centroid layout allows over 30 % reduction of the input offset voltage. The minimization of the input offset voltage, by increasing area of M1 and M2, causes degradation of the comparator speed, because it increases its input capacitance  $C_{\rm in}$ .

### 2.2.2 Propagation delay

Springer

In the filter in Fig. 1 the input signals propagate in parallel through the layers in the structure. The total

$$SR_B^+ = \frac{(n/4)I_{\text{bias}}}{2C_{gs13,14} + C_{db7} + C_{db8}}$$

(10a)

$$SR_B^- = \frac{nI_{\text{bias}}}{2C_{gs13.14} + C_{db7} + C_{db8}}$$

(10b)

The expressions (10a) and (10b) show, that the slew rate for a rising edge is four times smaller than the slew rate for a falling edge. The voltage swing  $\Delta V_A$  can be calculated bearing in mind that the full biasing current  $I_{\text{bias}}$  flows through M1, and as a result only M3 is active in the load circuit.

$$\Delta V_A = V_{gs3}|_{I_D = I_{\text{bias}}} - V_{gs3}|_{I_D = 0} = \sqrt{\frac{2I_{\text{bias}}}{\mu_0 C_{\text{OX}}(W/L)_3}}$$

(11)

where  $\mu_0$ ,  $C_{OX}$ , and (W/L) have their usual meanings. The worst case of the total propagation delay can be calculated using (9), (10a), (11), and (8). Assuming that:

Fig. 3 Monte Carlo histograms for input offset voltage: a (W/  $L)_{1,2} = 2/1$ , **b**  $(W/L)_{1,2} = 10/1$ ,  $c (W/L)_{1,2} = 50/1$ . For all cases  $(W/L)_{3-6} = 2/1$

Fig. 4 Monte Carlo histograms for input offset voltage: a separate M1 and M2, b M1 and M2 in common-centroid.  $(W/L)_{1,2} = 10/1, (W/L)_{3-6} =$

$(W/L)_{1,2} = 10 \mu \text{m}/1 \mu \text{m}, (W/L)_{3-6} = 2 \mu \text{m}/1 \mu \text{m}, I_{\text{bias}} =$ 10  $\mu$ A, and n = 2, the following results were obtained:  $\Delta V_A = 0.34 \text{ V}, SR_A = 61.7 \text{ V/}\mu\text{s}, \text{ and } SR_B^+ = 2270 \text{ V/}\mu\text{s}.$ The propagation delays for this case are  $t_{\text{delay},A} = 5.54 \text{ ns}$ , and  $t_{\text{delay},B} = 0.72$  ns. Finally, the analytically calculated value of the total propagation delay is  $t_{\text{delay}} = 6.26 \text{ ns}$ , whereas the delay determined based on the circuit simulation is 4.42 ns.

The delay time of the analog multiplexer can be resolved based on the time constant associated with the resistance  $r_{ds12-15}$  of the turned-on switches M12–M15 and the input capacitance  $C_{\rm in}$  of the comparator. Assuming that  $(W/L)_{12-15} = 1 \mu m/0.35 \mu m$ , the worst case of  $r_{ds12-15}$  is about 7–8 k $\Omega$ . The estimated input capacitance of the comparator for  $(W/L)_{1,2} = 10 \mu m/1 \mu m$  and  $(W/L)_{3-6} =$ 2 μm/1 μm is about  $C_{\rm in} \approx 120$  fF. The time constant for this case is about 0.95 ns, which means that the delay of the multiplexer is much smaller than the delay of the comparator.

A unique feature of the presented filter is that the comparator settling time has little influence on the video signal delay, and therefore the median filter is relatively fast. This is due to the fact that the outputs of the comparators control the switches and do not directly affect the video signals. As a

result, even if the output signals of the comparator has not yet reached the final value, the switches are correctly switched on. The only effect on switches, during the comparators settling time, is modulation of their on-resistance, which has minor effect on output video signals.

# 3 Implementation and measurements of a median filter

# 3.1 Filer implementation

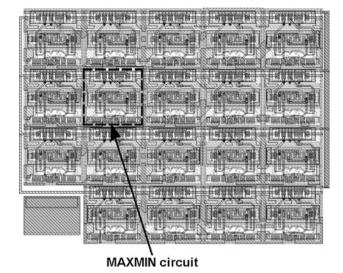

The median filter is designed to be implemented in AMS 0.35 µm CMOS technology. Based on the guidelines, given in the previous section, the MAXMIN circuits are optimised to reach a trade-off between accuracy and speed. To achieve a resolution equivalent to 7 bits for a video signal with 1.8 V amplitude, the filter resolution must be at least 14 mV. According to the histograms presented in Fig. 3(a), such a requirement can be satisfied if the width of the input transistors is greater or equal to 10 µm, in the case of M1 and M2 designed as separate devices. A better result is achievable, if the common-centroid technique is applied. In this case, as Fig. 3(b) shows, width of the transistors can be reduced to less than 10 µm. In the final circuit implementation, the transistors M1 and M2 were divided into four parts, and arranged in a common-centroid layout. The selected dimensions of the transistors are as follows:  $(W/L)_{1-2} = 10/1$ ,  $(W/L)_{3-6} = 2/1$ ,  $(W/L)_{7.9} =$ 4/1,  $(W/L)_{8,10} = 2/1$ ,  $(W/L)_{11} = 4/1$ ,  $(W/L)_{12-15} = 1/0.35$ . The biasing currents are established to be 10 µA for M11, and 5 µA for M8 and M10. The Monte Carlo analysis reveals that for the worst case, the voltage gain of a single comparator is 3,800 V/V, the input common-mode range is better than 2 V, and the input offset voltage is below 5 mV. The summary of the main electrical parameters of the MAXMIN circuit is given in Table 1. The layout of the MAXMIN circuit has dimensions 27  $\mu$ m  $\times$  27  $\mu$ m, and the layout of the overall median filter, consisting of 19 MAXMIN circuits, occupies 0.014 mm<sup>2</sup> area (Fig. 5).

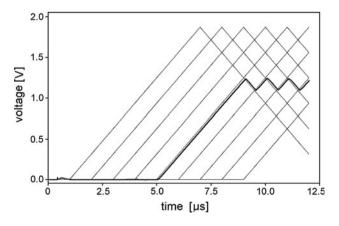

# 3.2 Measurements of electrical parameters

The operation of the median filter has been verified by means of simulations and measurements of a prototype integrated circuit. The simulated time response of the filter for a test signal is presented in Fig. 6. A set of nine triangle waveform signals (thin lines) is applied to the filter inputs. The succesive triangle signals are delayed by 1  $\mu$ s and have the same amplitude equal to 1.8 V. In this case, the filter is driven by many possible combinations of the inputs. The solid line, in Fig. 6, shows the output voltage of the filter, which correctly determines the median value, according to the formula (2).

Fig. 5 Layout of the median filter: width 135 μm, height 105 μm

The final filter resolution was also determined using a triangular waveform with 500 mV $_{pp}$  peak-to-peak value, and two DC voltages (200 and 500 mV) applied to three inputs of the filter. The remaining three inputs were connected to 0 V, and three to 1.8 V. Figure 7 shows the input and output waveforms for this case. The DC signals are omitted for clarity. Figure 7(a) shows a general view, whereas Fig. 7(b) presents a magnified portion of the waveforms, that shows the moment of the output switching. The plot in Fig. 7(b) clearly shows that the input offset voltage of the comparator is about 10 mV, which makes the relative resolution equal to 0.55 % (7 bits), for the input voltage range of 0–1.8 V.

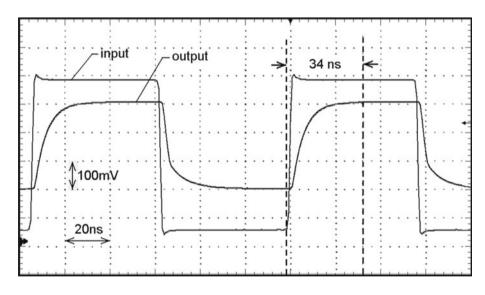

The measured dynamic properties of the filter were determined for the worst case. As Fig. 1 shows, the total delay time depends on a selection of the input signals combination, and it reaches its maximum when the input

Fig. 6 The output response of the median filter for triangle waveforms

Fig. 7 Osscilograms—the waveforms applied to determine the filter resolution: a measured waveforms, b zoomed area in the dashed circle

Fig. 8 Waveforms applied to determine the transmission delay

signals propagate through 9 MAXMIN circuits. A time response of the filter was measured for that case. Figure 8 presents the square wave input signal  $V_{i5}$  of 8.33 MHz frequency, and the output  $V_{out}$  of the filter. For the considered case, the total delay is about 34 ns. The delay is defined as a time interval between 1 % and 99 % of the initial and final values of the signal during its transition. This means that the achievable speed of an image reconstruction is 8.33 MP/s (Table 1).

Table 1 The simulated parameters of the MAXMIN circuit

| Technology CMOS                             | 0.35 μm AMS |

|---------------------------------------------|-------------|

| Supply voltage                              | 3.3 V       |

| Input offset (1 sigma)                      | 4.6 mV      |

| ICMR                                        | 0-2 V       |

| Total power consumption at 10 MHz $1V_{pp}$ | 54 μW       |

| Propagation delay time                      | 4.4 ns      |

| Comparator gain                             | 3800 V/V    |

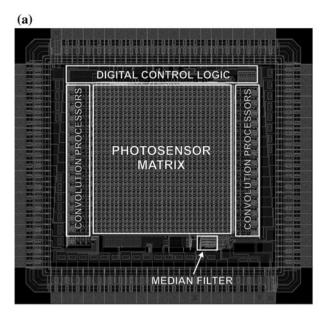

Fig. 9 Vision chip: a system architecture, b arrangement of a median filter and a pixel matrix

### 3.3 Image filtering example

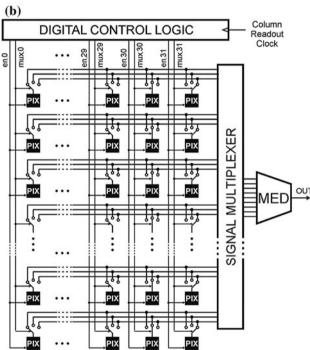

The presented median filter has been developed for use it in a prototype system with parallel processing of video images in real time. The system consists of a  $32 \times 32$  photopixel matrix and 32 analog convolution filters (Fig. 9a), which processes 2,000 frames per second. Due to the

limited area of the prototype integrated circuit, only a single median filter is implemented. The video signals from the matrix are sequentially directed to the median filter using a signal multiplexer, as shown in Fig. 9(b). For this reason, the maximum speed of median image processing is relatively low, about 30 frames per second. Based on simulation, the maximum speed of the median filtering is estimated to be about 1,600 frames per second if the parallel processing is used [24].

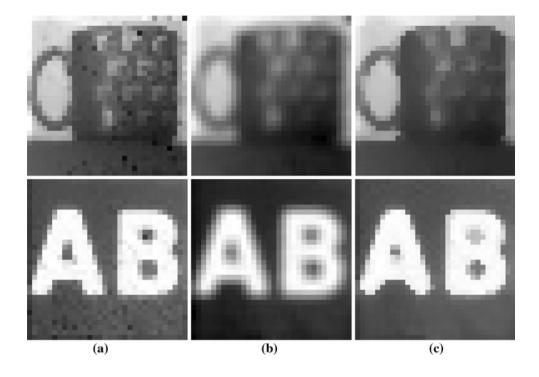

The raw images generated by a CMOS photo matrix are of low quality, due to the fixed pattern noise (FPN), random noise (RN), photo-response non-uniformity, and so called 'death' pixels (DP) [25]. An example of such an image is presented in Fig. 10(a). Without proper processing, this kind of image has little application in practice. One of the most frequently used methods for image enhancement are low-pass convolution filtering or median filtering. The sample results of processing, using the prototype image system and both types of filtering, are depicted in Fig. 10. As Fig. 10(b) shows, the convolution filtering reduces FPN and RN, but also causes an image blur, which in turn deteriorates the overall image quality. Significantly better results can be achieved with the median filtering (Fig. 10c), where after the removal of FPN, RN, and DP, the sharp edges of the object are preserved.

# 3.4 Comparison

The comparison of the proposed median filter to other analog solutions is summarized in Table 2. All the compared filters operate in continuous time, but they differ in the applied circuit technique and number of inputs. For example, in [4] the analog delay cells and comparators are used to implement a nine-input median filter. The references [2] and [5] present the filters which perform the bubble sort algorithm using current mirrors and current comparators. Another technique is used in [11] and [13], where three-input filters are designed using differential amplifiers, and a feedback. An interesting solution is presented in [14], where the authors propose a high precision four-input rank order filter based on gain-boosting amplifiers and voltage followers. A complete comparison of the filters is difficult, because in most of the published works, the authors do not specify a full set of filters parameters. Nevertheless, in terms of power consumption, accuracy, speed and area, our median filter is competitive to other solutions. Our circuit based on the MAXMIX selectors and the bubble sort topology is a bit more complicated than the other solutions, although the area needed for its

Fig. 10 Results of an exemplary image processing: a raw images, b low pass convolution filtering, c median filtering

**Table 2** Comparison of the selected median filters

|                         | This work      | [5]<br>2004 | [4]<br>2004 | [14]<br>2005 | [2]<br>2007 | [13]<br>1993   | [11]<br>1997 |

|-------------------------|----------------|-------------|-------------|--------------|-------------|----------------|--------------|

| No. of inputs           | 9              | 9           | 9           | 4            | 3           | 3              | 3            |

| Technology              | 0.35 μm        | 0.25 μm     | 2 μm        | 0.5 μm       | 0.35 μm     | 2 μm           | 2 μm         |

| Supply                  | 3.3 V          | 1.5 V       | 5 V         | 5 V          | 3.3 V       | 5 V            | 5 V          |

| Accuracy                | 10 mV (0.55 %) | 1.2 %       | NA          | 3 mV         | NA          | 10 mV (0.27 %) | NA           |

| Input range             | 0-1.8 V        | NA          | 0.7-1.5 V   | 3.5 V        | NA          | 0.8-4.5 V      | NA           |

| Power consumption       | 1.25 mW        | NA          | 14 mW       | 1 mW         | NA          | 5.6 mW         | 7 mW         |

| Delay time              | 34 ns          | 80 ns       | NA          | 33 ns        | NA          | NA             | 200 ns       |

| Area (mm <sup>2</sup> ) | 0.014          | NA          | 0.137       | 0.023        | 0.004       | NA             | 0.2          |

implementation is smaller. It is worth noting that the design procedure of our filter is easier, due to the fact that its main parameters, such as accuracy and speed, are easier to predict based on the comparator parameters. Also, our median filter is absolute stable, and has no DC offset problem in the output signal.

# 4 Conclusions

A low-power, high-speed, compact nine-input analog median filter based on a bubble sort network is presented. The operation of the designed filter has been carefully tested by means of simulations and measurements, performed with the use of a test vision system containing an integrated prototype vision-chip. The presented filter has advantages such as high processing speed and low power consumption. Its resolution is better than 0.55 %, the delay time is below 34 ns, and the total power consumption is 1.25 mW. The filter has a very compact layout and occupies a relatively small area equal to 0.014 mm<sup>2</sup>. Due to the small area and low power consumption, the filter is attractive for implementation of large, parallel, real-time image processing systems with a high computation rate.

Acknowledgments This work was supported in part by the Polish National Science Centre, under grant no. 2011/03/B/ST7/03547.

Open Access This article is distributed under the terms of the Creative Commons Attribution License which permits any use, distribution, and reproduction in any medium, provided the original author(s) and the source are credited.

#### References

- 1. Davies, E. R. (2005). Machine vision: Basic image filtering operations. Morgan Kaufmann: Elsevier.

- 2. Hung, Y.-C., Shieh, S.-H., & Tung, C.-K. (2007). A real-time current-mode CMOS analog median filtering cell for system-onchip applications. In Proceedings of the IEEE Conference on Electron Devices and Solid-State Circuits (EDSSC) (pp. 361–364).

- 3. Siskos, S. (2010). Low voltage analog median filters implementation. In Proceedings of the IEEE International Conference on Imaging Systems and Techniques (IST) (pp. 166-170).

- 4. Diaz-Sanchez, A., Ramirez-Angulo, J., Lopez-Martin, A., & Sanchez-Sinencio, E. (2004). A fully parallel CMOS analog median filter. IEEE Transactions on Circuits and Systems-II, 51(3), 116-123.

- 5. Huang, C.-Y., Wei, W.-H., & Liu, B.-D. (2004). Design of a 1.5 V analog current-mode median filter. In *Proceedings of the* Intelligent Sensors, Sensor Networks and Information Processing Conference (pp. 211-215).

- 6. Fikos, G., Vlassis, S., & Siskos, S. (2000). High-speed, accurate analogue CMOS rank filter. Electronics Letters, 36(7), 593-594.

- 7. Vlassis, S., & Siskos, S. (2003). Precision multi-input current comparator and its application to analog median filter implementation. Analog Integrated Circuits and Signal Processing, 34(3), 233–245.

- 8. Chartchai, N., Jintana, N., Boonying, K., Sorawat, C., & Kobchai, D. (2006). A CMOS median filter circuit design. In Proceedings of the International Symposium on Communications and Information Technologies (ISCIT '06) (pp. 1089-1092).

- 9. Poikonen, J., & Paasio, A. (2004). A ranked order filter implementation for parallel analog processing. IEEE Transactions on Circuits and Systems-I, 51(5), 974-987.

- 10. Hung, Y.-C., & Liu, B.-D. (2002). A 1.2-V rail-to-rail analog CMOS rank-order filter with k-WTA capability. Analog Integrated Circuits and Signal Processing, 32, 219–230.

- 11. Opris, I. E., & Kovacs, G. T. A. (1997). A high-speed median circuit. IEEE Journal of Solid-State Circuits, 32(6), 905-908.

- 12. Ramirez-Angulo, J., Carvajal, R. G., Ducoudray, G. O., Lopez-Martin, A. J., & Torralba, A. (2004). New compact CMOS continuous-time low-voltage analog rank-order filter architecture. IEEE Transaction on Circuits and Systems-II, 51(5), 257-261.

- 13. Dietz P. H., & Carley, L. R. (1993). An analog technology for finding the median. In Proceedings of the IEEE Custom Integrated Circuits Conference (pp. 611-614).

- 14. Carvajal, R. G., Ramirez-Angulo, J., Ducoudray, G. O., & Lopez-Martin, A. J. (2005). High-speed high-precision CMOS analog rank order filter with O(n) complexity. IEEE Journal of Solid-State Circuits, 40(6), 1238-1248.

- 15. Jimmy Li, J. S., & Harvey Holmes, W. (1988). Analog implementation of median filters for real-time signal processing. IEEE Transactions on Circuits and Systems, 35(8), 1032–1033.

- 16. Fitch, J. P., Coyle, E. J., & Gallagher, N. C. (1986). The analog median filter. IEEE Transactions on Circuits and Systems, 33(1),

- 17. Fahmy, S. A., Cheung, P. Y. K., & Luk, W. (2009). Highthroughput one-dimensional median and weighted median filters on FPGA. IET Computers & Digital Techniques, 3, 384-394.

- 18. Richards, D. (1990). VLSI median filters. IEEE Transactions on Acoustic, Speech and Signal Processing, 38, 145-153.

- 19. Chen, C.-T., Chen, L.-G., & Hsiao, J.-H. (1996). VLSI implementation of a selective median filter. IEEE Transactions on Consumer Electronics, 42(1), 36-42.

- 20. Yamasaki, H., & Shibata, T. (2007). A real-time image-featureextraction and vector-generation VLSI employing arrayed-shiftregister architecture. IEEE Journal of Solid-State Circuits, 42(9), 2046-2053.

- 21. Kinget, P., & Steyaert, M. (1997). Analog VLSI integration of massive parallel signal processing systems. Boston: Kluwer Academic Publishers.

- 22. Laker, K. R., & Sansen, W. M. C. (1994). Design of analog integrated circuits and systems. New York: McGraw-Hill.

- 23. Pelgrom, M. J. M., Duinmaijer, A. C. J., & Welbers, A. P. G. (1989). Matching properties of MOS transistors. IEEE Journal of Solid-State Circuits, 24(5), 1433-1439.

- 24. Jendernalik, W., Blakiewicz, G., Jakusz, J., Szczepanski, S., & Piotrowski, R. (2013). An analog sub-miliwatt CMOS image sensor with pixel-level convolution processing. IEEE Transactions on Circuits and Systems-I, 60(2), 279-289.

- Gamal, A. E., & Eltoukhy, H. (2005). CMOS image sensors. IEEE Circuits & Devices Magazine, May/June, 6-20.

W. Jendernalik was born in Starogard, Poland, in 1973. He received the M.Sc. and the Ph.D. degrees in electrical engineering from Gdansk University of Technology, Gdansk, Poland, in 1997 and 2006 respectively. From 2001 to 2006, he was a Research Assistant with the Department of Circuits, Electronic Gdansk University of Technology, where he worked in the field of continous-time analog filters. Since 2007 he has joined the

Department of Microelectronic Systems, as an Assistant Professor. His research interests include analog integrated circuits with emphasis on low-power vision processors and high-frequency analog filters.

G. Blakiewicz was born in Gorowo, Poland, in 1966. He received the M.Sc. and the Ph.D. degrees in electrical engineering from Gdansk University of Technology, Gdansk, Poland, in 1990 and 1997 respectively. From 1990 to 1997, he was a Research Assistant with the Department of Electronic Circuits, University of Technology, where he worked in the field of discrete-time analog filters. Since 1997 he has been an

Assistant Professor with the Department of Microelectronic Systems. From 2003 to 2004, he was a Visiting Assistant Professor in Electrical Engineering Department, Portland State University, working on analysis and optimization of substrate noise in mixed-signal SoCs. His main research interests include analog design with emphasis on low-voltage, low-power, and reduction of sensitivity to substrate

J. Jakusz was born in Poland in 1965. He received the M.Sc. and the Ph.D. degrees in electrical engineering from the Gdansk University of Technology, Gdansk, Poland, in 1990 and 2000 respectively. From 1990 to 1997, he was a Teaching and Research Assistant with the Department of Electronic Circuits, Gdansk University of Technology, where he worked in the field of analog integrated filter design. Since 2000 he has been an Assistant Professor with

the Department of Microelectronic Systems. His main research interests are in analog integrated circuits, vision processors and analog filters.

S. Szczepanski received the M.Sc. and Ph.D. (with honors) degrees in electronic engineering from Gdańsk University of Technology, Gdańsk, Poland, in 1975 and 1986 respectively. In 1986, he was a Visiting Research Associate with the Institute National Polytechnique de Toulouse (INPT), Toulouse, France. From 1990 to 1991, he was with the Department of Electrical Engineering, Portland State University, Portland, OR, on a Kosciuszko Foundation

Fellowship. From August to September 1998, he was a Visiting Professor with the Faculty of Engineering and Information Sciences at the University of Hertfordshire, Hatfield, U.K. He is currently an Associate Professor and Head of Department of Microelectronic Systems, Faculty of Electronics, Telecommunications and Informatics, Gdańsk University of Technology. He has published more than 120 papers and holds two patents. His teaching and research interests include circuit theory, fully integrated analog filters, high-frequency transconductance amplifiers, analog integrated circuit design in bipolar and CMOS technology, and current-mode analog signal