Postprint of: Lewicki A., Krzeminski Z., Abu-Rub H., Space-Vector Pulse width Modulation for Three-Level NPC Converter With the Neutral Point Voltage Control, IEEE Transactions on Industrial Electronics, Vol. 58, Iss. 11 (2011), pp. 5076-5086, DOI: 10.1109/TIE.2011.2119453

© 2011 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

# Space-Vector Pulse Width Modulation for Three-Level NPC Converter with the Neutral Point Voltage Control

Arkadiusz Lewicki, Zbigniew Krzeminski, Haitham Abu-Rub

Abstract— This paper proposes new space-vector pulse width modulation (SV-PWM) strategy for a three-level NPC inverter. The presented SV-PWM strategy makes it possible to control the neutral point voltage by optimum choice of switch sequence for any position and length of output voltage vector. The proposed solution takes into consideration the unbalance of the DC-link voltages. It also analyzes the influence of vector sequences on the predicted unbalance of the DC-link voltage. The solution allows selecting optimum vectors and their on-time durations in order to reduce quickly the DC-link voltage unbalance. The calculation of space vector area, proposed in this paper takes into consideration voltage unbalance and its influence on the length and position of vectors. The proposed approach assures properly generating the voltage output vectors, even in the case of the existing large voltage unbalance in the DC-link. Results of experimental investigation of the proposed modulation strategy are presented in the paper.

Index Terms— Multilevel Inverter, NPC Inverter, Pulse Width Modulation, Neutral Point Voltage Control

#### I. INTRODUCTION

MULTILEVEL inverter topologies are experiencing increased application in the industrial environment, particularly in high power drive systems [1, 2, 3, 4]. The main advantages of these inverters are improving quality of voltage waveforms and an increase in the DC-link voltage for a given blocking voltage capacity of the semiconductors. Generation of voltage vectors in multilevel inverters requires taking into consideration all the phenomena which have an influence on the accuracy of output vectors. While the neutral

Manuscript received September 29, 2010. Accepted for publication February 02, 2011.

Copyright © 2009 IEEE. Personal use of this material is permitted. However, permission to use this material for any other purposes must be obtained from the IEEE by sending a request to pubs-permissions@ieee.org

A. LEWICKI is with Electrical and Control Engineering Department, Gdansk University of Technology, ul. G. Narutowicza 11/12, 80-233 Gdansk, POLAND, (phone: +48-58-347-11-76; fax: +48-58-341-08-80; email: alewicki@ely.pg.gda.pl).

Z. KRZEMINSKI is with Electrical and Control Engineering Department, Gdansk University of Technology, ul. G. Narutowicza 11/12, 80-233 Gdansk, POLAND, (e-mail: zkrzem@ely.pg.gda.pl).

H. ABU-RUB is with the Electrical and Computer Engineering Department, Texas A&M University at Qatar, (e-mail: haitham.abu-rub@qatar.tamu.edu).

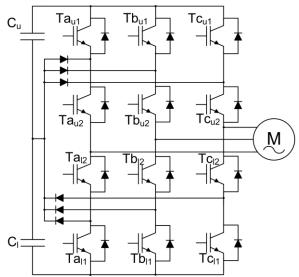

Fig. 1. Three-phase NPC inverter

point clamped (NPC) multilevel inverter (Fig.1) converts higher voltages using devices with lower rating, the DC-link voltage balancing problem seriously limits the applicability of these inverters, if not solved. The DC-link voltage unbalance causes an increase of voltage stress on switching devices and additional harmonic distortion in the inverter output voltage. To maximize the performance of three-level inverter, the voltages of the series connected DC-link capacitors should be equal.

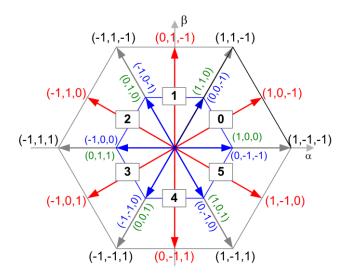

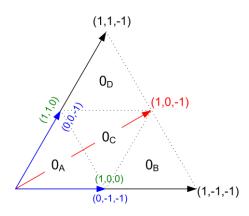

Different methods of DC-link voltage balance control are proposed in many papers [5, 6, 7, 8, 9, 10, 11, 12, 13, 14]. In most solutions of the PWM strategies, the lengths of active and passive vectors, with an assumption of balanced DC-link voltages, are calculated. This approach allows to divide the space vector area into six equal sectors (Fig.2). Each of them can be divided into equal subsectors. In many solutions of the SV-PWM strategies for three-level NPC inverter, one or two switching sequences are strictly assigned to specific subsectors [5, 6]. The control strategies of DC-link voltage balance are based on the change of switching sequences depending on the DC-link voltage unbalance [7, 15, 16, 17]. Most of the PWM solutions are based on using controllers to control neutral point voltages [8, 18, 19, 20, 21]. The duration of redundant vectors in the switching sequence is rearranged in order to reduce the

Fig. 2. Space vectors of three-level inverter in the case of DC-link balance:  $u_{cu}/u_{cl}=0.5/0.5$

voltage unbalance in the DC-link [7, 9, 15, 16, 22, 23, 24]. A similar solution was proposed in [25]. The voltage balance control strategy for one-phase NPC converter is based on the adjusting of effective time of the positive and the negative small vectors in response to the DC-link voltage unbalance and the direction of the load current.

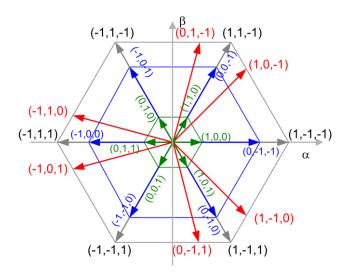

In the case of unbalanced DC-link voltages, the approach, based on assumption of equal voltages in the DC-link may be a reason of incorrect output voltage vector generation. A corrective method of vector duration dependent on the DClink voltage unbalance was proposed in [26]. The PWM strategy, proposed in [26], takes into consideration the influence of DC-link voltage unbalance on the length and position of active vectors in the space vector area. The DClink voltage unbalance is reduced by appropriate choice of redundant vectors due to direction of neutral point current and voltage unbalance on the DC-link capacitors. The calculation of active vectors duration considers the actual difference between voltages on upper and lower DC-link capacitors. The

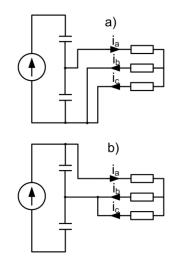

Fig.4. Influence of redundant vectors: (0,-1,-1) a) and (1,0,0) b) on DC-link voltages.

Fig.3 Space vectors of three level inverter in the case of DC-link unbalance occurrence:  $u_{cu}/u_{cl}=0,3/0,7$

influence on medium voltage vector, used in a switching sequence, on DC-link voltage unbalance is compensated in next steps of the proposed algorithm.

The modulation strategy, proposed in [27] for single-phase multilevel cascaded converter, takes into consideration movement of voltage vectors in switching sequence due to the voltage unbalance. The proposed solution makes it possible to properly generate an output voltage in the case of large voltage unbalance occurring on DC-link capacitors. The strategy to balance the DC-link voltages based on appropriate choice of switching sequence depends on the actual voltage unbalance and direction of output current.

A similar strategy for the DC-link unbalance compensation for three-phase NPC-converter was proposed in [28]. In this paper the influence of the DC-link unbalance on length and position of voltage vectors in three-dimensional control region was presented. The appropriate choice of switching sequence and duration times due to the DC-link voltages in [28] permits properly generating the converter output voltage.

The control of DC-link unbalance in NPC converter can be realized using different algorithms, proposed in many papers. The common property of these strategies is the application of redundant vectors as the "unbalance-controlled" vectors. The main limitations of commonly used strategies are:

-stiff sector division: only one switching sequence to any sector is assigned. It is not possible to choice other switching

TABLE I THE VOLTAGES BETWEEN A MOTOR CLAMP "X" (X=A,B,C) AND DC-LINK NEUTRAL POINT "N" AND THE ACTIVATION SIGNALS FOR "X" PHASE TRANSISTORS

| Activation signals for upper (u) and<br>lower (l) transistors in phase "x"<br>Tx <sub>u1</sub> ,Tx <sub>u2</sub> , Tx <sub>l2</sub> ,Tx <sub>l1</sub> | U <sub>xn</sub>  | Description of<br>transistor<br>state for a "x"<br>phase |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------|

| 1 , 1 , 0 , 0                                                                                                                                         | ucu              | 1                                                        |

| 0,0,1,1                                                                                                                                               | -uc <sub>l</sub> | -1                                                       |

| 0,1,1,0                                                                                                                                               | 0                | 0                                                        |

Fig.5. Sector and subsectors in space vector area.

sequence, which will reduce the voltage unbalance faster.

- no voltage unbalance prediction –commonly used strategies don't take into consideration the influence of medium vectors on DC-link voltage unbalance. The balancing algorithms are based on actual measured voltage unbalance, while it is possible to predict the voltage unbalance for any switching sequence before its activation,

- the activation times of redundant vectors are usually set by controllers. It is possible to precisely calculate the duration of compensation vectors.

In this paper a new SV-PWM strategy is proposed. The presented solution makes it possible to generate the desired inverter output voltage vector, independently of the DC-link voltage unbalance. The analysis of the DC-link voltage unbalance on parameters of voltage vectors in two-dimensional control region is realized. As distinct from other existing modulation strategies, the choice of vectors in switching sequence and the calculations of vector duration takes into consideration predicted voltage unbalance in the DC-link. The prediction algorithm for the DC-link voltage unbalance takes into consideration an influence of all active vectors in a switching sequence, before their activation. The prediction of voltage unbalance for all possible switching sequences is performed and the optimum switching sequence is realized.

The durations of redundant vectors are calculated in relation to the neutral point current, DC-link voltage unbalance, selected switching sequence, and DC-link capacity. The introduction of the DC-link capacity to the compensation algorithm allows calculating exact duration of redundant vectors, which makes the reduction of voltage unbalance very fast.

## II. PULSE WIDTH MODULATION FOR THREE-LEVEL NPC INVERTER

It is possible to switch-on only two transistors at the same time in any phase of a three-level NPC inverter. In the upper leg there are  $Tx_{u1}$ ,  $Tx_{u2}$ , in the lower leg:  $Tx_{12}$ ,  $Tx_{11}$ , and in the middle leg:  $Tx_{u2}$ , and  $Tx_{12}$ . ("x" denotes the inverter phase (a, b or c)). The voltages between the induction motor clamp and DC-link neutral point for any transistor combination and state

Fig.6. Proposed sector division of space vector area in the case of balance  $(u_{cu}/u_{cl}=0.5/0.5)$  a) and unbalance  $(u_{cu}/u_{cl}=0.3/0.7)$  b) of DC link voltages

description are presented in table 1. The length and position of large active vectors: (1,-1,-1), (1,1,-1), (-1,1,1), (-1,1,1), (-1,-1,1), (1,-1,1) and passive vectors: (111), (000), (-1,-1,-1) do not depend on the DC-link voltage unbalance. Activating these vectors has no influence on the DC-link unbalance occurrence. Activation of one of the redundant vectors: (1,0,0), (0, -1, -1), (1,1,0), (0,0,-1), (0,1,0), (-1,0,1), (0,1,1), (-1,0,0), (0,0,1), (-1,-1,0), (1,0,1), (0,-1,0) or one of medium active vectors (1,0,-1), (0,1,-1), (-1,0,1), (0,-1,1), (1,-1,0) connects the motor clamps to the DC-link neutral point and has an impact on the voltage change on DC-link capacitors (fig.4). The changes of voltages on upper and lower DC-link capacitors can be estimated from:

$$u_c(t) = \frac{1}{2C} \int_0^t i(\tau) d\tau + u_c(0), \qquad (1)$$

where *C* - DC-link capacity ( $C=C_u=C_l$ ),  $u_c$  - voltage on the upper capacitor of DC-link,  $i(\tau)$  – neutral point current,  $\tau$  - the duration of redundant or medium vectors.

The amplitude and position of the redundant and medium vectors depend on the DC-link voltage unbalance (Fig.2 and Fig.3). Activating one of the medium vectors gives no possibility to full control of neutral point voltage - the length of medium vector, used in switching sequence, depends on position and amplitude of the inverter output voltage. The direction of the neutral point current can be controlled only if redundant vectors are used in switching sequence - the direction of neutral point current can be changed by substituting redundant vector for an equivalent vector. For example, during activation of redundant vector (0,-1,-1), the "a" phase current is a neutral point current. Positive current direction charges the upper capacitor and discharges the lower capacitor in the DC-link. The substitution of redundant vector (0,-1,-1) for an equivalent vector (1,0,0) will cause discharging of the upper capacitor and charging of the lower one (Fig. 4). Typical switching sequence contains two or more redundant vectors. The switching sequences, proposed in [7]

$$(1,0,0) \to (1,0,-1) \to (0,0,-1) \to (0,-1,-1),$$

(2)

$$(1,1,0) \to (1,0,0) \to (1,0,-1) \to (0,0,-1),$$

(3)

contains a pair of redundant vectors: (0,0,-1) in (2) and (1,0,0) in (3), which have an opposite influence on DC-link voltage balance. The control of neutral current can be done by choosing one of sequences (2)-(3), depending on the DC-link voltage unbalance.

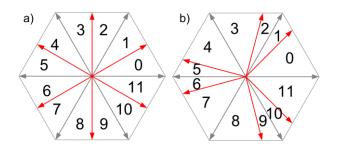

In the SV-PWM strategies for three-level inverters, the space vector area is usually divided into six sectors, limited by large active vectors (Fig.2) . Each sector can be divided into subsectors, as shown in Fig. 5 [5, 6, 29, 30]. In many solutions of SV-PWM strategies, the switching sequences are strictly defined for subsectors. For example, in [6] the switching sequences for subsectors  $0_A-0_C$  were defined as:

$0_A$ :

$$(-1, -1, -1) \to (0, -1, -1) \to (0, 0, -1) \to (0, 0, 0) \to (1, 0, 0) \to (1, 1, 0) \to (1, 1, 1)$$

(4)

0<sub>B</sub>:

$$\begin{pmatrix} 0, -l, -l \end{pmatrix} \to (l, -l, -l) \to (l, 0, -l) \to (l, 0, 0), \quad (5)$$

$$\begin{array}{c} 0_{\mathrm{C}}:\\ (0, -l, -l) \to (l, 0, 0) \to (l, 0, 0), \quad (1, 0, 0) \to (1, 0, 0), \quad (5) \end{array}$$

$$(0,-1,-1) \to (0,0,-1) \to (1,0,-1) \to (1,0,0) \to (1,1,0), (6)$$

In this case, the neutral-point voltage can be controlled by rearranging the duration of redundant vectors [6, 7, 16, 22]. The neutral point voltages can be adjusted using controllers [8], where the difference between voltage on the upper  $u_{cu}$  and lower  $u_{cl}$  capacitors (fig.1):

$$\Delta u = u_{Cu} - u_{Cl} , \qquad (7)$$

is used as a feed-back signal.

### III. PROPOSED SV-PWM STRATEGY

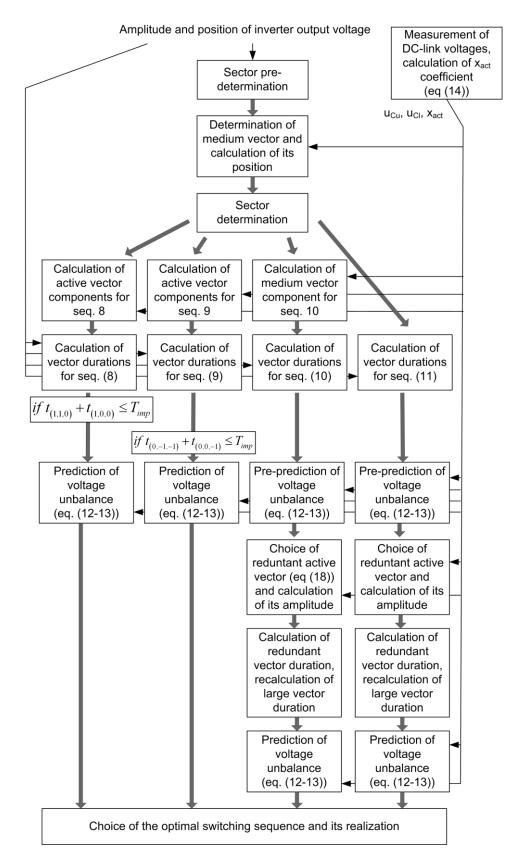

In three-phase NPC inverters the amplitude and position of active vectors depend on the DC-link voltage unbalance. The sector division proposed in this paper takes into account the change of position and length of the active vector. The space vector area contains twelve sectors, as shown in Fig.6. This approach properly assigns a position of the output voltage vector to a sector, even in the case of large unbalance in DClink. This strategy requires recalculation of the lengths and positions of the redundant and medium vectors and requires redefinition of the sectors for any PWM cycle. For any of the sectors, there are four switching sequences defined. The vector durations are calculated simultaneously for four sequences. For example, if an output voltage vector takes a position in "0" sector, the durations are calculated for the following sequences:

$$(0,0,0) \to (1,1,0) \to (1,0,0) \to (0,0,0), \tag{8}$$

$$(0,0,0) \to (0,-1,-1) \to (0,0,-1) \to (0,0,0), \quad (9)$$

$$(0,0,0) \to (1,-1,-1) \to (1,0,-1) \to (0,0,0), \quad (10)$$

$$(0,0,0) \to (1,-1,-1) \to (1,1,-1) \to (0,0,0).$$

(11)

The switching sequence (11) utilizes only vectors which have no influence on the DC-link voltage balance.

Sequences (8) and (9) contain the active vectors, which have an influence on DC-link voltage unbalance. Activating of these sequences will increase or decrease the voltage unbalance, depending on neutral-point current direction. The amplitude of active vectors, utilized in (8), depends on the voltage on upper capacitor, while the amplitude of active vectors in seq. (9) depends on the voltage on lower capacitor. The amplitude of output voltage vector, generated using sequences (8)-(9), depends on the unbalance of the DC-link voltages and doesn't depend on the output voltage vector position (Fig.3). This permits choosing one of the sequences (8)-(9) in the case of voltage unbalance occurrence, if the amplitude of inverter output voltage is higher than half of the DC-link voltage. The sequences (8)-(9) may be used only in case if the inverter output voltage vector can be inscribed into hexagon, bounded by ends of vectors (1,1,0), (1,0,0),(1,0,1), (0,0,1), (0,1,1), (0,1,0) (for seq.(8)) and vectors (0,0,-1), (0,-1)1,-1, (0,-1,0), (-1,-1,0), (-1,0,0), (-1,0,-1) (for seq.(9)) (fig. 3). None of these sequences can be used if their activation increases the DC-link voltage unbalance.

Sequence (10) contains only one vector, which has an influence on the DC-link voltage balance. Additionally, the position and amplitude of the medium vector (1,0,-1) depend on voltage unbalance (fig.3). The vector components of (1,0,-1) vector can be calculated as:

$$u_{\alpha(1,0,-1)} = \sqrt{\frac{2}{3}} \left( u_{Cu} + \frac{1}{2} \cdot u_{Cl} \right),$$

$$u_{\beta(1,0,-1)} = \frac{\sqrt{2}}{2} u_{Cl}.$$

(12)

Vector components of all active and passive vectors for 3-level NPC inverter can be calculated using following equations:

$$u_{\alpha} = \sqrt{\frac{I}{6}} \cdot \begin{pmatrix} u_{Cu} \cdot \begin{pmatrix} 2 \cdot (Ta_{u1} \cdot Ta_{u2}) - \\ (Tb_{u1} \cdot Tb_{u2}) - (Tc_{u1} \cdot Tc_{u2}) \end{pmatrix} \\ -u_{Cl} \cdot \begin{pmatrix} 2 \cdot (Ta_{l2} \cdot Ta_{l1}) - \\ (Tb_{l2} \cdot Tb_{l1}) - (Tc_{l2} \cdot Tc_{l1}) \end{pmatrix} \end{pmatrix}, \quad (13)$$

$$u_{\beta} = \sqrt{\frac{I}{2}} \cdot \begin{pmatrix} u_{Cu} \cdot ((Tb_{u1} \cdot Tb_{u2}) - (Tc_{u1} \cdot Tc_{u2})) \\ -u_{Cd} \cdot ((Tb_{l2} \cdot Tb_{l1}) - (Tc_{l2} \cdot Tc_{l1})) \end{pmatrix},$$

Where  $Tx_{(u,l)(1,2)}$  denotes the signals of transistor activation in phase x (x=(a,b,c)). The values of Tx are: 1 – if transistor is switched-on, 0 – if transistor is switched-off. For example:  $Ta_{u1}=1$  denotes that the first upper transistor in phase "a" is switched on (fig.1)

The choice of switching sequence has to ensure proper generation of the output voltage vector, as well as the minimization of the DC-link voltage unbalance. The control strategy of neutral point voltage should take into consideration the influence of switching sequence on DC-link voltage. For any of the sequences (8)-(11) an unbalance criterion "x" is calculated:

| Sector | Sequence<br>number | Base sequence                                                                                                                                                                                 | Sequence with redundant vectors                                                                                                          |

|--------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | (8)                | $(0,0,0) \to (1,1,0) \to (1,0,0) \to (1,0,0) \to (0,0,0)$                                                                                                                                     |                                                                                                                                          |

|        | (9)                | $ \begin{pmatrix} 0,0,0 \end{pmatrix} \rightarrow \begin{pmatrix} 0,-1,-1 \end{pmatrix} \rightarrow \\ \begin{pmatrix} 0,0,-1 \end{pmatrix} \rightarrow \begin{pmatrix} 0,0,0 \end{pmatrix} $ |                                                                                                                                          |

|        | (10)               | $(0,0,0) \to (1,-1,-1) \to (1,0,-1) \to (0,0,0)$                                                                                                                                              | $ (0,0,0) \to (0,-1,-1) \to (1,-1,-1) \to (1,0,-1) \to (0,0,0) $<br>or<br>$ (0,0,0) \to (1,-1,-1) \to (1,0,-1) \to (1,0,0) \to (0,0,0) $ |

|        | (11)               | $(0,0,0) \rightarrow (1,-1,-1) \rightarrow (1,1,-1) \rightarrow (0,0,0)$                                                                                                                      | $ (0,0,0) \to (0,-1,-1) \to (1,-1,-1) \to (1,1,-1) \to (0,0,0) $<br>or<br>$ (0,0,0) \to (1,-1,-1) \to (1,1,-1) \to (1,1,0) \to (0,0,0) $ |

| 3      | (8)                | $ (0,0,0) \to (0,1,0) \to (1,1,0) \to (0,0,0) $                                                                                                                                               |                                                                                                                                          |

|        | (9)                | $ \begin{pmatrix} 0,0,0 \end{pmatrix} \rightarrow \begin{pmatrix} -1,0,-1 \end{pmatrix} \rightarrow \\ (0,0,-1) \rightarrow \begin{pmatrix} 0,0,0 \end{pmatrix} $                             |                                                                                                                                          |

|        | (10)               | $(0,0,0) \to (-1,1,-1) \to (0,1,-1) \to (0,0,0)$                                                                                                                                              | $ (0,0,0) \to (-1,0,-1) \to (-1,1,-1) \to (0,1,-1) \to (0,0,0) $<br>or<br>$ (0,0,0) \to (-1,1,-1) \to (0,1,-1) \to (0,1,0) \to (0,0,0) $ |

|        | (11)               | $ \begin{pmatrix} 0,0,0 \end{pmatrix} \rightarrow \begin{pmatrix} 1,1,-1 \end{pmatrix} \rightarrow \\ \begin{pmatrix} -1,1,-1 \end{pmatrix} \rightarrow \begin{pmatrix} 0,0,0 \end{pmatrix} $ | $ (0,0,0) \to (1,1,0) \to (1,1,-1) \to (-1,1,-1) \to (0,0,0) $<br>or<br>$ (0,0,0) \to (1,1,-1) \to (-1,1,-1) \to (-1,0,-1) \to (0,0,0) $ |

TABLE II

THE REDUNDANT VECTORS INTRODUCED TO SWITCHING SEQUENCES FOR SECTORS 0 AND 3

$$x = x_{pred} + x_{act}, \tag{14}$$

where:  $x_{pred}$  is the predicted unbalance criterion, calculated for sequences (8)-(11), before their activation:

$$x_{pred} = \sum_{k=1}^{n} t_k \cdot i_k, \,, \tag{15}$$

$i_k$  is the neutral point current, specified for k-th vector in considered switching sequence,  $t_k$  is the duration of k-th vector, n – is a number of vectors in a switching sequence.

The  $x_{act}$  specifies an actual voltage unbalance on the DC-link capacitors and can be determined from (1) as:

$$x_{act} = i_x \cdot t_x = 2 \cdot C \cdot \Delta u , \qquad (16)$$

where:  $t_x$  is the time to balance the voltages in DC-link, when the neutral point current is equal to  $i_x$ .  $\Delta u$  is a difference between voltages in the DC-link (7).

The switching sequence (10) is used if the voltage output vector cannot be generated using sequences (8)-(9) because of

its amplitude and possibility to voltage unbalance reduction. If the criterion:

$$x = \sum_{k=1}^{n} t_k \cdot i_k + x_{act} = 0, \qquad (17)$$

is not fulfilled, the redundant vectors should be introduced to (10). The switching sequence (10) can be rewritten as:

$$\begin{array}{l} (0,0,0) \to (0,-1,-1) \to (1,-1,-1) \\ \to (1,0,-1) \to (0,0,0) \end{array},$$

(18)

or

depending on the sign of "x" coefficient and direction of the neutral point current:

Fig.7. Graphical representation of proposed algorithm

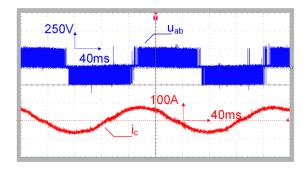

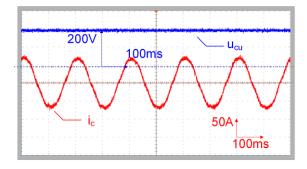

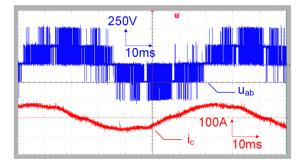

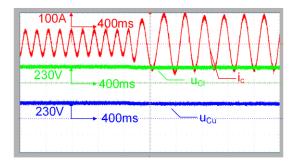

Fig.8. The converter output voltage  $u_{ab}$  and phase current  $i_c$  during generation of converter output voltage, Fundamental frequency:5[Hz], Uout=69V, DC-link voltage Udc=520V

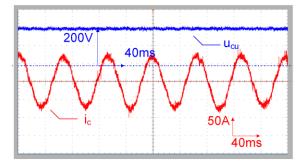

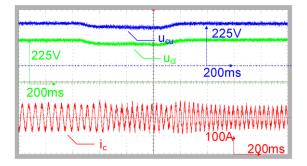

Fig.10. The voltage on upper capacitor of DC-link  $u_{cu}$  and phase current  $i_c$  during generation of converter output voltage, Fundamental frequency:5[Hz] , Uout=69V, DC-link voltage Udc=400V

$$\begin{array}{c} i_{(1,0,0)} < 0, x > 0\\ or\\ i_{(1,0,0)} > 0, x < 0 \end{array} \right\} \Rightarrow (1,0,0), \\ i_{(0,-1,-1)} < 0, x > 0\\ or\\ i_{(0,-1,-1)} > 0, x < 0 \end{array} \right\} \Rightarrow (0,-1,-1)$$

$$(20)$$

where  $i_{(0,-1,-1)}$  and  $i_{(1,0,0)}$  are neutral point currents during activation of (0,-1,-1) and (1,0,0) redundant vector respectively. In the presented case, the neutral point current is equal to:

$$i_{(0,-1,-1)} = i_a \\ i_{(1,0,0)} = -i_a$$

(21)

where *i*<sub>a</sub> is an "a" phase current.

The position of (0,-1,-1) and (1,0,0) vectors overlaps the position of (1,-1,-1) vector. The duration of redundant vector can be calculated as:

$$t_{(0,-I,-I),(1,0,0)} = abs\left(\frac{x}{i_{(0,-I,-I),(1,0,0)}}\right),$$

(22)

Fig.9. The converter output voltage  $u_{ab}$  and phase current  $i_c$  during generation of converter output voltage, Fundamental frequency:15[Hz], Uout=207V, DC-link voltage Udc=520V

Fig.11. The voltage on upper capacitor of DC-link  $u_{cu}$ , and phase current  $i_c$  during generation of converter output voltage, Fundamental frequency:15[Hz], Uout=207V, DC-link voltage Udc=400V

where  $t_{(0,-1,-1)}$  and  $t_{(1,0,0)}$  are the durations of redundant vectors (0,-1,-1) and (1,0,0) respectively. Activation of redundant vector for calculated time will reduce the unbalance of the DC-link voltages to zero. Introduction of the additional redundant vector to the switching sequence demands correction of the duration of the large, active vector (1,-1,-1). The new duration of the vector (1,-1,-1) can be calculated from:

$$t'_{(1,-I,-I)} = t_{(1,-I,-I)} - t_{(0,-I,-I),(1,0,0)} \cdot \left(\frac{u_{\alpha(0,-I,-I),(1,0,0)}}{u_{\alpha(1,-I,-I)}}\right), \quad (23)$$

where  $t_{(1,-1,-1)}$ ,  $t_{(0,-1,-1)}$ ,  $t_{(1,0,0)}$ : durations of (1,-1,-1), (0,-1,-1), (1,0,0) vectors respectively,  $u_{\alpha(0,-1,-1)}$ ,  $u_{\alpha(1,0,0)}$ ,  $u_{\alpha(1,-1,-1)}$ , - an  $\alpha$  component of (1,-1,-1), (0,-1,-1), (1,0,0) vectors in  $\alpha,\beta$  coordinate system,  $t'_{(1,-1,-1)}$  – new duration of large vector (1,-1,-1).

If the duration of redundant vector, calculated from (22) is too long, the new duration of vector (1,-1,-1) will be negative. In this case the duration of redundant vector should be reduced to:

$$t_{(0,-1,-1),(1,0,0)} = t_{(1,-1,-1)} \frac{u_{\alpha(1,-1,-1)}}{u_{\alpha(0,-1,-1),(1,0,0)}},$$

(24)

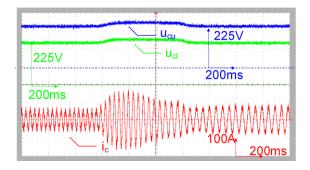

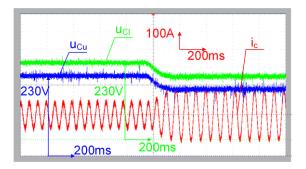

Fig.12. The voltage on upper  $u_{cu}$  and the lower  $u_{cL}$  capacitor of DC-link  $u_{cu}$  and phase current  $i_c$  during speed change of induction motor from 0.6 to 0.4 pu, , DC-link voltage Udc=450V

Fig.14. The voltage on upper  $u_{cu}$  and the lower  $u_{cL}$  capacitor of DC-link  $u_{cu}$  and phase current  $i_c$  during load change from 0.05 to 0.45 pu, Fundamental frequency: 5[Hz], DC-link voltage Udc=460V

and the duration of vector (1,-1,-1) should be set to zero. Appropriate switching sequence can be rewritten as:

$$(0,0,0) \to (0,-1,-1) \to (1,0,-1) \to (0,0,0),$$

(25)

$$(0,0,0) \rightarrow (1,0,-1) \rightarrow (1,0,0) \rightarrow (0,0,0).$$

(26)

In this case, the unbalance of the DC-link voltages will be reduced during a few pulse periods.

If the new duration of vector (1,-1,-1) is positive and a sum of all vectors in the switching sequence is higher than a pulse period:

$$t_{(0,-1,-1),(1,0,0)} + t_{(1,0,-1)} + t'_{(1,-1,-1)} > T_{imp}, \qquad (27)$$

the duration of redundant vector should be reduced to assure the criterion:

$$t'_{(1,-1,-1)} = T_{imp} - \left(t'_{(0,-1,-1),(1,0,0)} + t_{(1,0,-1)}\right),$$

(28)

where  $t'_{(0,-1,-1)}$  and  $t'_{(1,0,0)}$  are the new, reduced duration of redundant vectors (0,-1,-1) and (1,0,0). At the same time, the next criterion should be fulfilled:

Fig.13. The voltage on upper  $u_{cu}$  and the lower  $u_{cL}$  capacitor of DC-link  $u_{cu}$  and phase current  $i_c$  during speed change of induction motor from 0.4 to 0.6 pu, , DC-link voltage Udc=450V

Fig.15. The voltage on upper  $u_{cu}$  and the lower  $u_{cL}$  capacitor of DC-link  $u_{cu}$  and phase current  $i_c$  during load change from 0.05 to 0.45 pu, Fundamental frequency: 15[Hz], DC-link voltage Udc=460V

$$\frac{t_{(1,-1,-1)}}{T_{imp}} \cdot u_{\alpha(1,-1,-1)} =$$

$$\frac{t_{(1,-1,-1)}}{T_{imp}} \cdot u_{\alpha(1,-1,-1)} + \frac{t_{(0,-1,-1),(1,0,0)}}{T_{imp}} \cdot u_{\alpha(0,-1,-1),(1,0,0)}$$

(29)

where  $T_{imp}$  is a pulse period.

The new duration of redundant vector ((0,-1,-1) or (1,0,0)) can be calculated by the substitution of (28) to (29):

$$t'_{(0,-1,-1),(1,0,0)} = (T_{imp} - t_{(1,-1,-1)} - t_{(1,0,-1)}) \cdot \frac{u_{\alpha(1,-1,-1)}}{u_{\alpha(1,-1,-1)} - u_{\alpha(0,-1,-1),(1,0,0)}},$$

(30)

The negative value of  $t'_{(0,-1,-1)}$  or  $t'_{(1,0,0)}$  denotes that the amplitude and position on inverter output voltage makes the introduction of redundant vector impossible. The inverter output vector using sequence (10) will be generated.

The redundant vector can also be introduced to (11) sequence. The algorithm for duration calculation will be performed in the same manner as that proposed for the switching sequence (10). In the case of the DC-link voltage unbalance, the switching sequence (11) can be performed as

or

$$\begin{array}{l} (0,0,0) \to (0,-1,-1) \to (1,-1,-1) \\ \to (1,1,-1) \to (0,0,0) \end{array} ,$$

(31)

or

$$(0,0,0) \to (1,-1,-1) \to (1,1,-1) \to (1,1,0) \to (0,0,0),$$

(32)

depending on the sign of "x" coefficient and direction of the neutral point current.

The choice of one switching sequence from (8)-(10) is based on minimization of the unbalance criterion.

The second calculation of unbalance criterion (14) takes into consideration all redundant vectors introduced to the switching sequences and their calculated durations. This solution makes it possible to choose an optimum switching sequence in order to reduce voltage unbalance in the DC-link. The modified switching sequence (11) can be used instead of (10) in two cases. The first - if the predicted unbalance criterion (14), calculated for (11) sequence, has a lower value in comparison with the same criterion calculated for the (10) sequence (all sequences contain redundant vectors). The second - if the unbalance criterion (14), calculated for (10) sequence (including redundant vectors) is higher than:

$$x_{max} = 2 \cdot C \cdot \varDelta u_{max} \,, \tag{33}$$

where  $\Delta u_{max}$  is a maximum allowed difference between voltages on the upper and lower DC-link capacitors.

The sequences (31)-(32) contain only one redundant vector which has an influence on the DC-link voltage balance. These sequences can be used for the control of DC-link voltage balance in the case of large amplitude of the inverter output voltage or large voltage unbalance in the DC-link.

On Fig. 7 the graphical representation of proposed algorithm is presented. Table 1 presents the redundant vectors introduced to switching sequences (8)-(11) for sectors 0 and 3.

#### IV. MINIMIZATION OF COMUTATION NUMBER

The number of commutations in the proposed PWM strategy can be reduced by the appropriate choice (or elimination) of passive vectors. Switching sequences (8)-(11) can be rewritten as:

$$(1,1,1) \to (1,1,0) \to (1,0,0) \to (0,0,0),$$

(34)

$$(-1,-1,-1) \to (0,-1,-1) \to (0,0,-1) \to (0,0,0),$$

(35)

$$(-1, -1, -1) \to (1, -1, -1) \to (1, 0, -1) \to (1, 1, 1),$$

(30)

$$(-1, -1, -1) \to (1, -1, -1) \to (1, 1, -1) \to (1, 1, 1).$$

(37)

Introducing an additional redundant vector to (36) gives the sequence:

$$\begin{array}{ccc} t_{pasiv} & t_{(0,-l,-l)} & t_{(l,-l,-l)} \\ (-1,-1,-1) \to (0,-1,-1) \to (1,-1,-1) \to \\ t_{(1,0,-l)} & t_{pasiv} \\ (1,0,-1) \to (0,0,0) \end{array}$$

(38)

or

$$\begin{array}{ccc} t_{pasiv} & t_{(0,-1,-1)} \\ (-1,-1,-1) \to (1,-1,-1) \to \\ t_{(1,0,-1)} & t_{(1,0,0)} & t_{pasiv} \\ (1,0,-1) \to (1,0,0) \to (0,0,0) \end{array}$$

(39)

where  $t_{pasiv}$  is a duration of passive vector,  $t_{(0,-1,-1)}$ ,  $t_{(1,-1,-1)}$ ,  $t_{(1,0,-1)}$ ,  $t_{(1,0,-1)}$ ,  $t_{(1,0,0)}$  are durations of active vectors.

The switching sequence (38) can be replaced by the sequence:

$$\begin{array}{ccc} t_{pasiv}' & t_{(0,-l,-l)} + \Delta t_{r} & t_{(0,-l,-l)}' \\ (-1,-1,-1) \to (0,-1,-1) \to (1,-1,-1) \to \\ t_{(1,0,-l)} & \Delta t_{r} & t_{pasiv}' \\ (1,0,-1) \to (1,0,0) \to (0,0,0) \end{array}$$

(40)

and the sequence (39) by following:

$$\begin{array}{ccc} t_{pasiv} & \Delta t_r & t_{(0,-l,-l)} \\ (-1,-1,-1) \to (0,-1,-1) \to (1,-1,-1) \to \\ t_{(1,0,-l)} & t_{(1,0,0)} + \Delta t_r & t_{pasiv} \\ (1,0,-1) \to (1,0,0) \to (0,0,0) \end{array}$$

(41)

Both redundant vectors (0,-1,-1) and (1,0,0) have an opposite influence on the DC-link voltage balance. The duration of redundant vector is elongated for the same time, denoted as  $\Delta t_r$ .

For the switching sequences (40) and (41) the same criterion (42) have to be fulfilled:

$$t_{(1,-1,-1)} \cdot u_{\alpha(1,-1,-1)} = \Delta t_r \cdot u_{\alpha(0,-1-1)} + \Delta t_r \cdot u_{\alpha(1,0,0)}, \quad (42)$$

+ $t_{(1,-1,-1)}' \cdot u_{\alpha(1,-1,-1)}$

where  $t_{(1,1,-1)}$  is an actual duration and  $t_{(1,1,-1)}$ ' is the new duration of (1,-1,-1) vector.

Because:

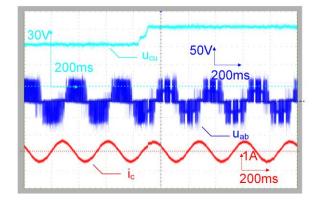

Fig.16. The voltage on upper capacitor of DC-link  $u_{cu}$ , converter output voltage  $u_{ab}$  and phase current  $i_c$  in case of voltage imbalance reduction. Fundamental frequency:3[Hz], Uout=24V, DC-link voltage Udc=60V

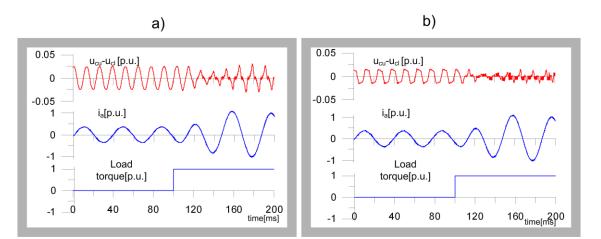

Fig.17 Result of simulation on classic SV-PWM strategy with PI controller utilized to DC-link voltage balancing a) and proposed SV-PWM strategy with prediction of DC-link voltage unbalance b). The difference between upper and lower capacitor voltages ( $u_{cu}$ - $u_{cl}$ ), the converter output current ( $i_a$ ) in case of load torque changes (from 0 to nominal). The maximum allowed voltage difference for proposed SV-PWM strategy (33):  $\Delta u_{max}$ =5V

$$u_{\alpha(1,-1,-1)} = u_{\alpha(0,-1-1)} + u_{\alpha(1,0,0)}, \quad (43)$$

the criterion (42) can be rewritten as:

$$t_{(1,-1,-1)} = \Delta t_r + t_{(1,-1,-1)}', \qquad (44)$$

The next criterion should be fulfilled:

$$t_{(1,-1,-1)} + 2 \cdot t_{pasiv} = 2 \cdot \Delta t_r + \left(t_{(1,-1,-1)}' + 2 \cdot t_{pasiv}'\right), \quad (45)$$

where  $t_{pasiv}$  is a duration and  $t_{pasiv}$  is a new duration of passive vectors in sequences (40)-(41).

By substitution (44) to (45), the duration  $\Delta t_r$ . and the new duration of (1,-1,-1) vector can be calculated:

$$\Delta t_r = 2 \cdot \left( t_{pasiv} - t_{pasiv}' \right), \tag{46}$$

$$t_{(1,-1,-1)}' = t_{(1,-1,-1)} - \Delta t_r, \qquad (47)$$

where new duration of passive vector  $t_{pasiv}$ , have to be chosen according to criterion

$$t_{pasiv} \ge t_{pasiv}' \ge t_{pasiv} - \frac{t_{(1,-1,-1)}}{2}.$$

(48)

#### V. SIMULATION AND EXPERIMENTAL RESULTS

The used experimental system consists of three-level inverter and three-level controlled rectifier with DC-link capacitances  $C_u=C_l=7.2mF$ , two DSP control boards for generating the PWM control signals for both converters, and unloaded induction motor with the parameters:  $P_n=160kW$ ,  $U_n=690V$ ,  $I_n=161A$ ,  $\cos\phi=0.87$ , f=50Hz. The PWM sampling period  $T_{imp}$  was equal to 150µs (the Carrier frequency: 3.33kHz). The speed of the induction motor was controlled in

sensorless closed loop mode. Proposed SV-PWM strategy was used in both converters, but the control systems of converters weren't coupled. Fig. 8 and Fig.9 show the output voltage and phase current during generation of inverter output voltage when fundamental frequency is 5Hz and 15 Hz respectively. Fig 10 and 11 show the voltage on the upper capacitor of DClink and phase current for the same fundamental frequencies. Fig 12 and 13 show the voltages on both capacitors and phase current during speed change of induction motor. The voltages on both DC-link capacitors during load change on fig 14 and 15 are presented. The difference between capacitor voltages, during experimental investigations, didn't exceed 5V. The voltage drop (shown on fig 15) is an effect of controllers' limits on rectifier control system. Such limit has been chosen not to exceed the current rating of the existing fuses.

Fig.16 presents transients of DC-link voltage, inverter phase current and output voltage in the case of voltage unbalance reduction. In this case the unbalance of DC-link voltages was forced by introducing of a non-zero value of  $\Delta u_f$  component into equation:

$$\Delta u = u_{Cu} - u_{Cl} + \Delta u_f , \qquad (49)$$

which is used for determining the DC-link voltage unbalance. This experimental investigation (fig 16) was carried out for reduced DC-link voltage ( $u_{dc}$ =60 V) and unloaded 1.5kW induction motor. DC-link capacitances were equal to  $C_u$ =C<sub>1</sub>=500µF.

The comparison of the proposed SV-PWM strategy and a SV-PWM strategy with PI controller-balanced DC-link voltages was realized by simulation and presented on fig 17a and 17b. The inverter parameters are: DC-link capacitance – 2 series connected capacitors (500 $\mu$ F each), DC-link voltage 564V (1.41 p.u). The model used is the NPC inverter supplies an induction motor with parameters: P=1.5kW, Un=400V, In=3.5A. Sampling period T<sub>imp</sub>=150 $\mu$ s. Motor control strategy – scalar control U/f=const with commanded frequency 18Hz. In both SV-PWM strategies, the sector division of space

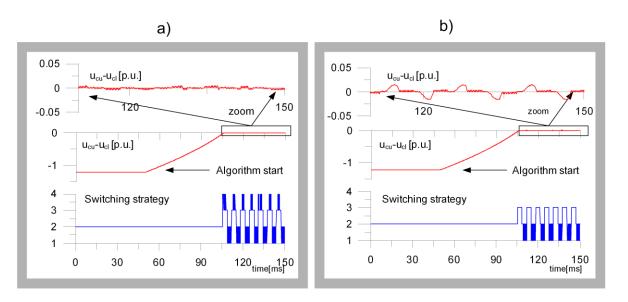

Fig.18. Result of simulation on proposed SV-PWM strategy. The difference between an upper and lower capacitor voltages ( $u_{cu}$ - $u_{cl}$ ) and used switching strategy (1- sequence (8), 2 - sequence (9), 3-sequence (10), 4- sequence (11) in case of unbalance, for maximum allowed voltage difference (33)  $\Delta u_{max}$ =0.5V a) and  $\Delta u_{max}$ =10V b)

vector area takes into account the position and amplitude of active vectors, as shown in Fig. 6. The switching sequences, used in SV-PWM strategy with PI balance controller, contain two redundant vectors. For sector "0" there are redundant vectors (0,-1,-1) and (1,0,0) with durations  $t_{(0,0,-1)}$  and  $t_{(1,0,0)}$  respectively:

$$\begin{array}{l} (0,0,0) \to (0,-1,-1) \to (1,-1,-1) \\ \to (1,0,-1) \to (1,0,0) \to (0,0,0) \end{array} , \tag{50}$$

The durations of redundant vectors are equal to:

$$t_{(0,-1,-1)} = \frac{t_a}{2} \cdot (1+f),$$

$$t_{(1,0,0)} = \frac{t_a}{2} \cdot (1-f), , \qquad (51)$$

$$f \in \langle -1, 1 \rangle$$

Where  $t_a$  – the duration of both redundant vectors in a switching sequence, f- control factor set by DC-link balance controller.

#### VI. CONCLUSION

In this paper a new SV-PWM strategy for 3-level NPC converter is proposed. In the proposed solution, the division of space vector area into sectors is based on the analysis of position and length of boundary vectors. It allows properly generating the inverter output voltage, even in the case of large voltage unbalance in the DC-link. Proposed modulation strategy takes into consideration voltage unbalance, neutral point current and DC-link capacitance for determining the duration of redundant vector in switching sequence. For each of the twelve sectors, four alternative switching sequences are

defined. The optimum choice of one of switching strategies is based on the analysis of predicted voltage unbalance for any sequence, including their capability of reducing the voltage unbalance. Choice of the redundant vectors introduced to switching sequences and selection of their durations makes the reduction of voltage unbalance very fast.

The proposed PWM strategy, similarly to other control strategies, utilizes redundant active vector in switching sequence in order to reduce the DC-link voltage unbalance. The main differences are in selecting methods of redundant vector duration. The prediction of voltage unbalance allows reducing the voltage unbalance before its occurrence.

Additionally, in the proposed method it is possible to use four alternative switching strategies to reduce voltage unbalance as fast as possible. In most cases the balancing of DC-link voltages relies on using one of three sequences (seq. 8-10). The maximum voltage unbalance, which makes it possible to activate sequence (11), can be set by equation (33). Figures 18a and 18b show the difference between an upper and lower capacitor voltages ( $u_{cu}$ - $u_{cl}$ ), and utilized modulation strategy in case of large DC-link unbalance occurrence for  $\Delta u_{max}$ = 0.5V and  $\Delta u_{max}$ =10V respectively. The motor load was set to 0.5 p.u, however the rest of simulation parameters were the same as used for fig.17.

#### REFERENCES

- Krug D., Bernet S., Fazel S. S, Jalili K., Malinowski M., Comparison of 2.3-kV Medium-Voltage Multilevel Converters for Industrial Medium-Voltage Drives, IEEE Transactions on Industrial Electronics, Vol. 54, No. 6, (2007).

- [2] Franquelo L. G., Rodriguez J. L., Leon J., Kouro S., Portillo R., Prats M.A., "The age of multilevel converters arrives", IEEE Industrial Electronics Magazine, Vol. 2, Issue 2, (2008).

- [3] Fazel S., Bernet S., Krug D., Jalili K., "Design and Comparison of 4-kV Neutral-Point-Clamped, Flying-Capacitor, and Series-Connected H-Bridge Multilevel Converters", IEEE Transaction on Ind. Electronics, Vol. 43, No. 4, (2007)

- [4] Abu-Rub, H., Holtz, J., Rodriguez, J., and Baoming, G., "Medium Voltage Multilevel Converters - State of the Art, Challenges and Requirements in Industrial Applications", IEEE Transactions on Industrial Electronics, Vol. 57, No. 8, (2010).

- [5] Lai Y., Chou Y., Pai S.. "Simple PWM Technique of Capacitor Voltage Balance for Three-Level Inverter with DC-link Voltage Sensor Only", The 33rd Annual Conference of the IEEE Industrial Electronics Society IECON (2007)

- [6] Bhalodi K.H., Agrawal P, "Space Vector Modulation with DC-Link Voltage Balancing Control for Three-Level Inverters", International Conference on Power Electronics, Drives and Energy Systems, PEDES (2006)

- [7] Suh J., Choi Ch. Hyun D.: A new simplified space-vector PWM method for three-level inverters, 14 Annual Applied Power Electronics Conference and Exposition, APEC, (1999),

- [8] Portillo R.C., Prats M. M., León J.I., Sánchez J. A., Carrasco J.M., Galván E., Franquelo L. G., Modeling Strategy for Back-to-Back Three-Level Converters Applied to High-Power Wind Turbines, IEEE Transactions on Industrial Electronics, Volume 53, No. 5, (2006)

- [9] Seo J.H, Choi H. Ch.: Compensation for the neutral-point potential variation in three-level space vector PWM, Sixteenth Annual IEEE Applied Power Electronics Conference and Exposition, APEC (2001)

- [10] Schweizer, Mario; Friedli, Thomas; Kolar, Johann W.,, Comparison and implementation of a 3-level NPC voltage link back-to-back converter with SiC and Si diodes, 25 IEEE Applied Power Electronics Conference and Exposition APEC, (2010).

- [11] Zaragoza, J.; Pou, J.; Ceballos, S.; Robles, E.; Jaen, C.; Corbalan, M.; Voltage-Balance Compensator for a Carrier-Based Modulation in the Neutral-Point-Clamped Converter, IEEE Transactions on Industrial Electronics, Volume: 56, Issue: 2., (2009)

- [12] Enli Du; Ligao He; Xu Li; Yanlin Ma; Neutral point potential balance of three-level inverter based on parameters self-tuning fuzzy logic control strategy, 36th Annual Conference on IEEE Industrial Electronics Society, IECON (2010),

- [13] Ghennam T, Berkouk E.M., Francois B.; A Novel Space-Vector Current Control Based on Circular Hysteresis Areas of a Three-Phase Neutral-Point-Clamped Inverter, IEEE Transactions on Industrial Electronics, Volume: 57, Issue: 8 (2010)

- [14] Pulikanti, S.R.; Dahidah, M.S.A.; Agelidis, V.G; Voltage Balancing Control of Three-Level Active NPC Converter Using SHE-PWM, IEEE Transactions on Power Delivery, Volume: 26, Issue: 1(2011)

- [15] Holtz J., Oikonomou N., Neutral Point Potential Balancing Algorithm at Low Modulation Index for Three-Level Inverter Medium Voltage Drives, Industry Applications Conference IAS, (2005),

- [16] Holtz J., Oikonomou N., "Neutral point potential balancing algorithm at low modulation index for three-level inverter medium voltage drives," IEEE Transaction on Industrial Electronics Vol. 43, No. 3, (2007).

- [17] Malinowski M., Stynski S., Kolomyjski W., Kazmierkowski M. P., "Control of Three-Level PWM Converter Applied to Variable-Speed-Type Turbines", IEEE Transaction On Industrial Electronics, vol. 56, no. 1, pp. 69-77, (2009).

- [18] Pereira, I.; Martins, A.;,, Neutral-point voltage balancing in three-phase NPC converters using multicarrier PWM control, International Conference on Power Engineering, Energy and Electrical Drives, (2009)..

- [19] Pereira, I.; Martins, A.; "Multicarrier and space vector modulation for three-phase NPC converters: A comparative analysis", 13th European Conference on Power Electronics and Applications EPE, (2009)

- [20] Umbría, F.; Gordillo, F.; Salas, F.; Vázquez, S.; Voltages balance control in three phase three-level NPC rectifiers, IEEE International Symposium on Industrial Electronics ISIE (2010)

- [21] Alloui, H.; Berkani, A.; Rezine, H.; A three level NPC inverter with neutral point voltage balancing for induction motors Direct Torque Control, XIX International Conference on Electrical Machines ICEM, (2010),

- [22] Seo J.H., Choi CH.H., Hyun D.S." A New Simplified Space–Vector PWM Method for Three-Level Inverters", IEEE Transaction On Power Electronics, vol. 16, no.4. (2001)

- [23] Patel, P.J.; Patel, R.A.; Patel, V.; Tekwani, P.N.; "Implementation of Self Balancing Space Vector Switching Modulator for Three-Level Inverter", IEEE Region 10 and the Third international Conference on Industrial and Information Systems, ICIIS (2008),

- [24] Zhu Rong-wu, Wu Xiao-jie, Jiang Xiao-yan, Dai Peng; An Improved Neutral-Point-Potential Balance Control Strategy for Three-level PWM Rectifier, Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics, (2010)

- [25] Zhang Zhi; Xie Yun-xiang; Huang Wei-ping; Le Jiang-yuan; Chen Lin; A new SVPWM method for single-phase three-level NPC inverter and the control method of neutral point voltage balance, International Conference on Electrical Machines and Systems. ICEMS (2009).

- [26] Pou J., Boroyevich D., Pindado R., New Feedforward Space-Vector PWM Method to Obtain Balanced AC Output Voltages in a Three-Level Neutral-Point-Clamped Inverter, IEEE Transactions on Industrial Electronics, vol. 49, no. 5, (2002),

- [27] Leon, J.I.; Vazquez, S.; Watson, A.J.; Franquelo, L.G. Wheeler, P.W.; Carrasco, J.M. ,,Feed-Forward Space Vector Modulation for Single-Phase Multilevel Cascaded Converters With Any DC Voltage Ratio, IEEE Transactions on Industrial Electronics, Volume 56, Issue 2, (2009)

- [28] Leon, J.I.; Vazquez, S.; Portillo, R.; Franquelo, L.G.; Carrasco, J.M.; Wheeler, P.W.; Watson, A.J.,,Three-Dimensional Feedforward Space Vector Modulation Applied to Multilevel Diode-Clamped Converters, IEEE Transactions on Industrial Electronics, Volume 56, Issue 1, (2009)

- [29] Tamai S, Koyama M., Furii T., Mizoguchi S., Kawabata T. : 3 Level Gto Inverter-Inverter Pair System For Large Capacity Induction Motor Drive, Fifth European Conference on Power Electronics and Applications, (1993).,

- [30] Shinohara K., Sakasegawa E., A New PWM Method with Suppressed Neutral Point Potential Variation of Three Level Inverter for AC Servo Motor Drive., IEEE International Conference on Power Electronics and Drive Systems, PEDS'99 Hong Kong (1999).

Arkadiusz Lewicki received the M.Sc. and Ph.D. degrees in electrical drives from the Faculty of Electrical Engineering, Gdansk University of Technology, Gdansk, Poland in 1998 and 2003, respectively. He is currently with the Institute of Automatic Control of Electric Drives, Gdansk University of Technology. His scientific activities are concentrated on microprocessor control of converters, pulse width modulation techniques, and nonlinear control.

**Zbigniew Krzeminski** received the Ph.D. degree from the Technical University of Łodz, Łodz, Poland, in 1983 and the D.Sc. degree from Silesian Technical University, Gliwice, Poland, in 1991. From 1993 he is a Professor of Electrical Engineering at Gdansk University of Technology. His main areas of research interests are modeling and simulation of electric machines, control of high performance electric drives and signal processor based control systems.Prof. Z. Krzeminski is author of over 130 articles, 2 books and 6 patents. Main

achievements of prof. Z. Krzeminski is development of multiscalar models of the induction motor, which are generalized form of known vector model, and invention of variable observer for the induction motor used in sensorless drives.

Haitham Abu-Rub (M'99–SM'07) received the M.Sc. degree in electrical engineering from the Gdynia Maritime University, Poland, in 1990 and the Ph.D. degree from Gdansk University of Technology, Poland, in 1995, in which he was later on hired as assistant professor.

For eight years, he has been hired as an Assistant Professor and as an Associate Professor at Birzeit University, Palestine. For four years, he has been appointed the Chairman of Electrical Engineering

Department at the same university for four years. He is currently an Associate Professor with Texas A&M University at Qatar. His main research interests include electric drives and power electronics.

Dr. Abu-Rub is the recipient of many prestigious international awards, such as the American Fulbright Scholarship (at Texas A&M University), the German Alexander von Humboldt Fellowship (at the University) of Wuppertal), the German DAAD Scholarship (at Bochum University), the British Royal Society Scholarship (at Southampton University), and others. Dr. Abu-Rub has published more than one hundred journal and conference papers.